您好!歡迎光臨烜芯微科技品牌官網(wǎng)!

- 收藏烜芯微

- 手機訪問

掃一掃訪問手機網(wǎng)站 - 在線留言

- 網(wǎng)站地圖

傳真:

18923864027

QQ:

709211280

地址:

深圳市福田區(qū)振中路84號愛華科研樓7層

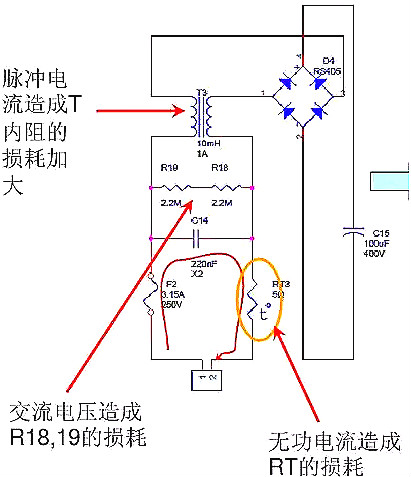

開關(guān)電源待機功耗問題要怎么解決圖解開關(guān)電源是一種高頻化電能轉(zhuǎn)換裝置,是電源供應器的一種。其功能是將一個位準的電壓,透過不同形式的架

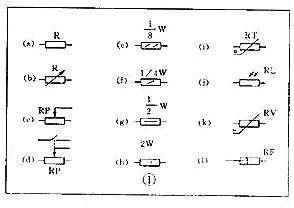

常用電子元器件符號-全面的電路圖符號大全什么是電子元件本文主要是介紹電子元器件符號大全。電子元件(electronic component),是電子電

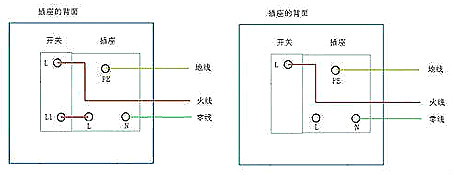

電路故障分析和定位的常用方法總結(jié)電路故障分析-常見的幾種電路故障電,在我們生活中的應用比較廣泛,它給我們的生活帶來了很多的便利,我

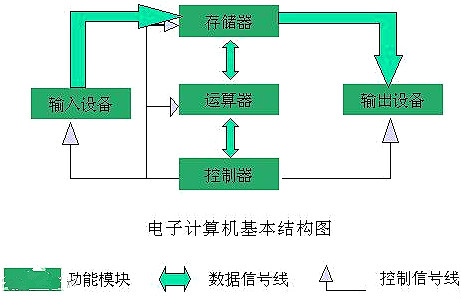

最全硬件測試的5個流程圖文詳解硬件最全的硬件測試5個流程圖文詳解,硬件(英文名Hardware)是計算機硬件的簡稱(中國大陸及香港用語,臺灣

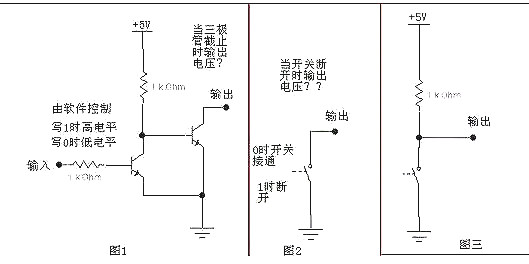

各種IO輸出類型與如何區(qū)分-電路基礎知識什么是IO各種IO輸出的類型及如何區(qū)分,I O輸入 輸出(Input Output),分為IO設備和IO接口兩個部分。

開關(guān)電源各種波形的由來-開關(guān)電源波形圖解開關(guān)電源本文主要講開關(guān)電源各種波形的由來。開關(guān)模式電源(Switch Mode Power Supply,簡稱SM

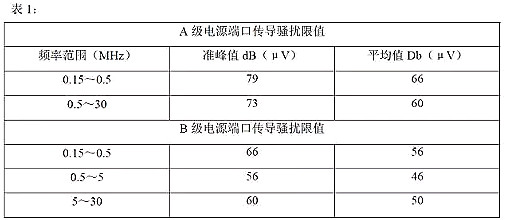

開關(guān)電源的傳導、輻射分析與圖解開關(guān)電源的傳導與輻射的概述開關(guān)電源的傳導與輻射,目前,電子產(chǎn)品電磁兼容問題越來越受到人們的重視,尤其

電路設計誤區(qū)的14項解析及模擬電路設計注意事項在解析電路設計誤區(qū)之前,我們先來看看電子電路設計基本流程。1、先分析所要實現(xiàn)的功能,并

電容-從10個方面匯總電容知識(作用、參數(shù)、公式等)什么是電容?電容(Capacitance)亦稱作電容量,是指在給定電位差下的電荷儲藏量,記為

原理圖符號大全與怎么將原理圖符號畫得通俗易懂原理圖概念原理圖符號,本文主要是講如何將原理圖符號畫得通俗易懂?由原理圖延伸下去會涉及

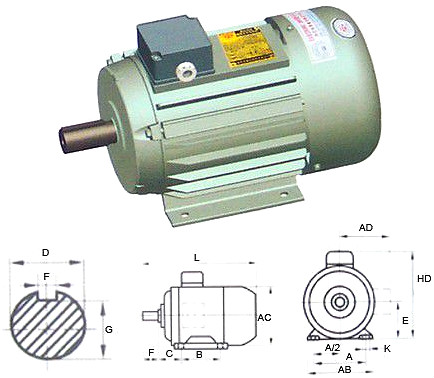

三相異步電動機接線圖與正反轉(zhuǎn)接線實圖解三相異步電動機三相異步電動機接線圖及正反轉(zhuǎn)接線實圖講解,三相異步電機,是感應電動機的一種,是

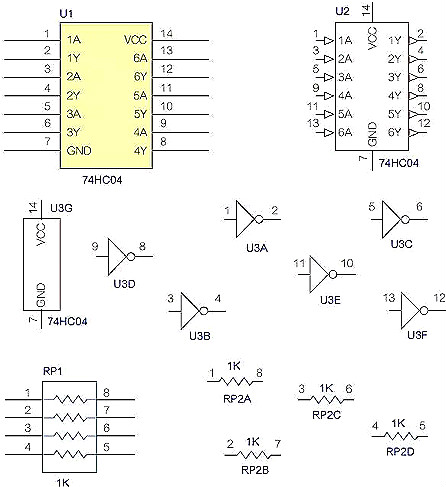

集成電路IC是否工作的準確判斷方法解析IC集成電路概述集成電路(integrated circuit,港臺稱之為積體電路)是一種微型電子器件或部件。采