在中大功率電源中,現(xiàn)在市面上最流行的拓撲結構可謂是移相全橋和LLC了,工程師們也最喜歡將這它們放在一塊作比較,這是由于它們的原邊MOS管都可以實現(xiàn)ZVS,從而降低損耗,提高了功率密度。但它們也各有不同的優(yōu)缺點,這里我們來分析一下移相全橋的工作特點,而LLC在前段時間發(fā)的中已分析過,這里就不再詳細描述。

移相全橋,顧名思義,首先它的硬件拓撲是一個全橋結構,而“移相”的意思是控制方式采用移相方式。我們知道PWM和PFM的控制原理,那么“移相”控制的控制原理是什么呢?接下來,我們就此說道說道。

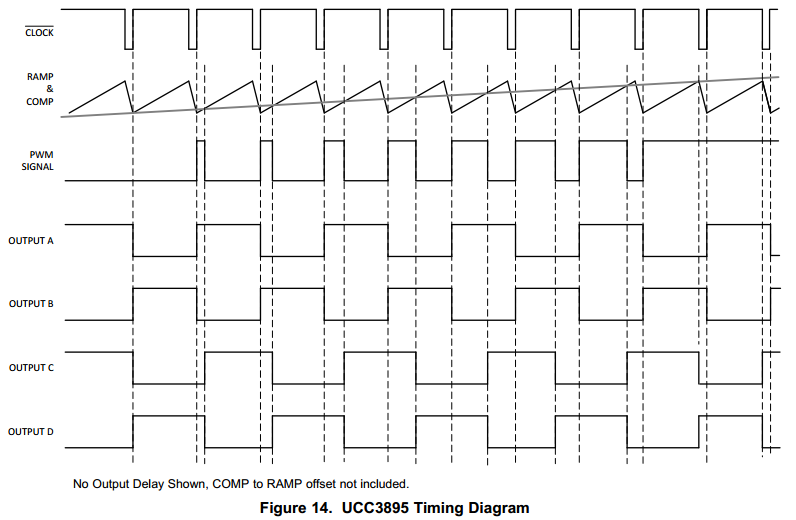

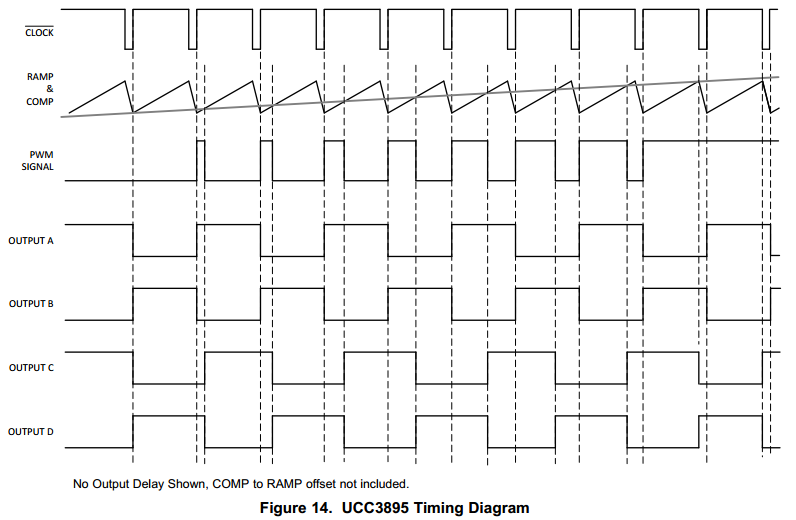

UCC2895是經(jīng)典的移相全橋控制芯片,圖1是它datasheet中的時序圖。CLOCK是芯片的時鐘,決定了芯片工作頻率;RAMP與環(huán)路輸出的COMP信號做比較,決定移相角度大小PWM SIGNGAL,PWM SIGNAL占空比為0時,移相角度為180°,占空比為100%時,移相角度為0。

圖1

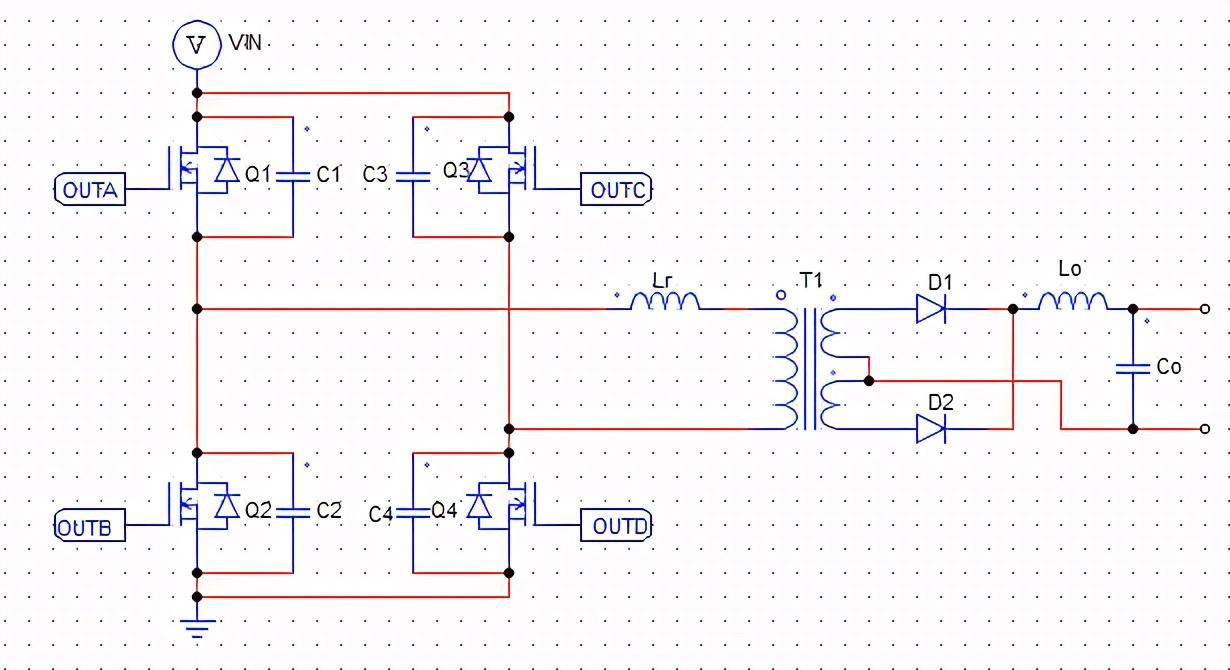

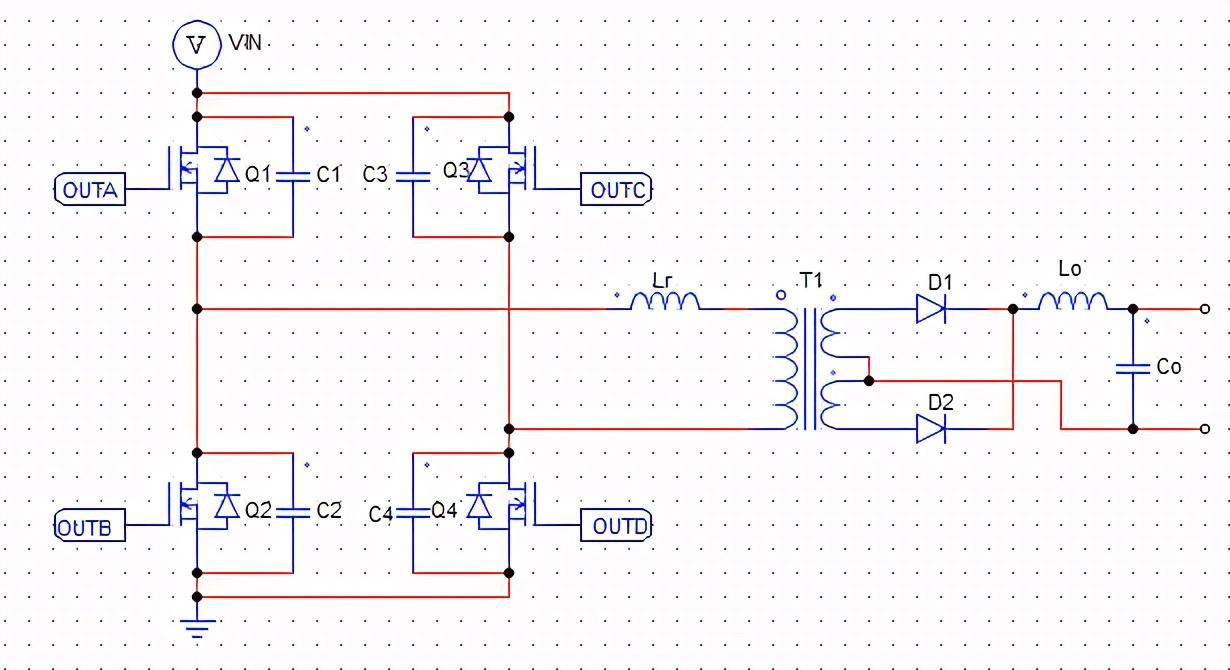

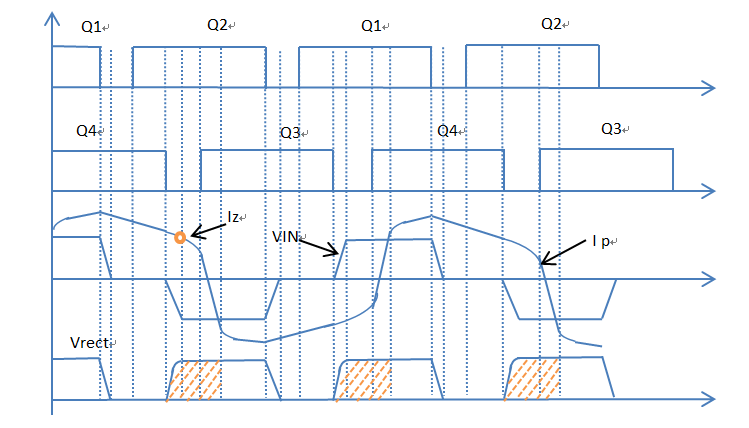

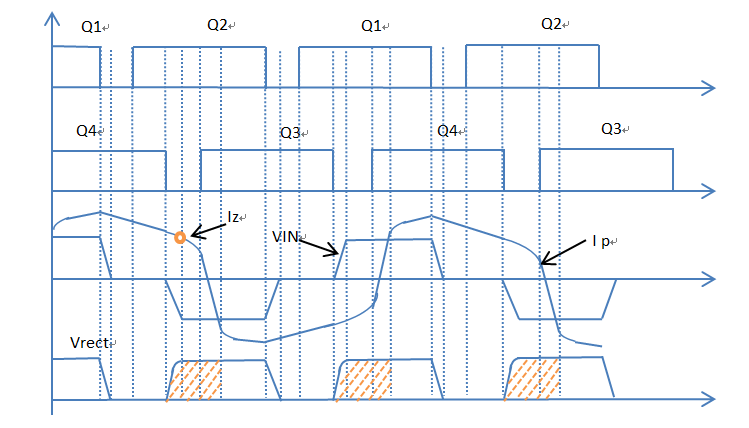

圖2是驅(qū)動的信號的接對應MOS管的驅(qū)動方法。在PWM驅(qū)動方式控制中,一般是直接控制對管的Q1/Q4、Q2/Q3的驅(qū)動信號占空比大小。而在移相方式中,不直接改變單個開關管的驅(qū)動占空比,而是保持每個開關管驅(qū)動占空比為50%,通過改變驅(qū)動信號相位的方式來改變對管同時導通時間,從而調(diào)節(jié)輸出。所以實際上“移相”也是一種特殊PWM控制方式。

圖1中,OUTPUTA/OUTPUTB相位超前于OUTPUTC/OUTPUTD,所以我們稱圖2中的Q1和Q2為超前橋臂,Q3和Q4為滯后橋臂。超前橋臂比滯后橋臂更容易實現(xiàn)ZVS,這是為什么呢,后面將會作出解釋。

圖2

圖3

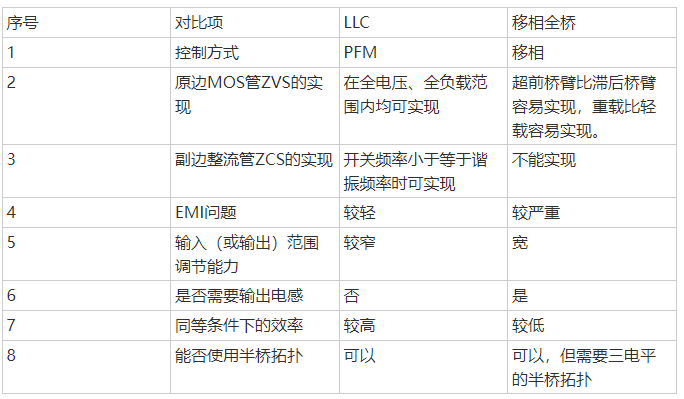

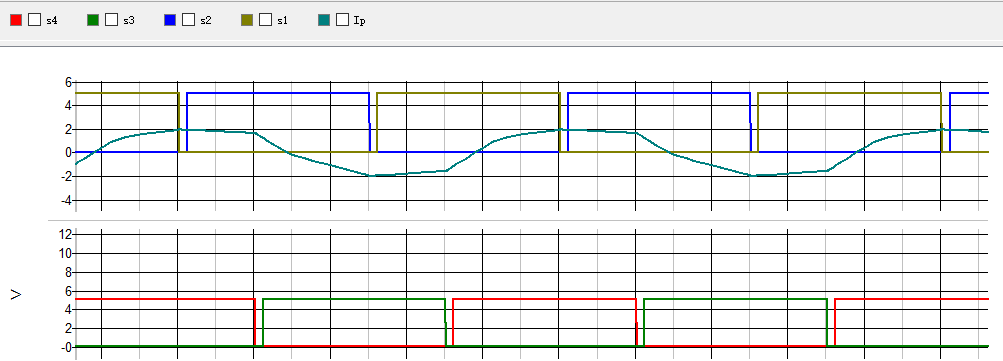

圖3展示了移相全橋工作的實現(xiàn)波形圖,其中Ip為諧振腔的電流,Vrect為變壓器副邊電壓,其值等于VIN/N,N為變壓器匝比。Vrect波形的陰影部分是丟失的波形,即在實際中這部分時間沒有能量傳遞到輸出,相當于這部分MOS管的占空比被間接丟失了,導致有效占空比變小,這在設計時應該考慮補償占空比。

為什么會出現(xiàn)這種現(xiàn)象呢?這是因為這個時間段的原邊電流較小,不足于提供輸出電流,而副邊電感維持輸出電流使得D1、D2均導通,相當于副邊繞組短路。隨著下一組對管的同時導通,電流迅速增大到一定值才能將能能量傳遞到輸出。而此時原邊電流增大的速率與諧振電感Lr大小有關,Lr越大,電流增大的速率越小,使得丟失的占空比越大,所以Lr越小越好?討論這個問題時,我們會涉及到前文提到的“超前橋臂比滯后橋臂更容易實現(xiàn)ZVS”的問題。

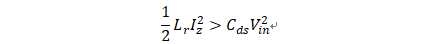

首先我們要知道原邊MOS管是如何實現(xiàn)ZVS的,它是通過電感電流不能斷續(xù)的特性來抽取MOS管寄生電容Cds的電能,以此使得在MOS管開通前Vds降為0。例如,圖2中,Q1關斷后,Lr電流繼續(xù)流向變壓器,在Q2開通前,其電流回路只能通過C1和C2,此時,C1是充電,C2是放電。其實這個時候,不僅是Lr參與抽取電流,輸出電感Lo通過變壓器映射到原邊也參與抽取電流,但對于Q3、Q4的關斷時刻,由于丟失占空比,副邊繞組相當于短路Lo不能映射到原邊,不參與抽取電流,所以Q3、Q4相比于Q1、Q2更難實現(xiàn)ZVS。

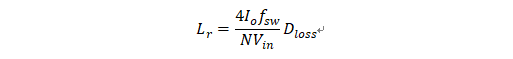

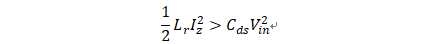

綜上,諧振電感Lr太大會導致丟失占空比嚴重,不利于調(diào)節(jié)控制;Lr太小不利于實現(xiàn)原邊MOS管的ZVS,所以在設計時需要綜合考量,選擇適合Lr。一般可以通過以下兩個方程選擇Lr的的大小。

其中,Dloss為丟失占空比,fsw為開關頻率,Io為輸出電流。

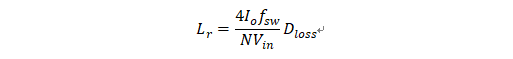

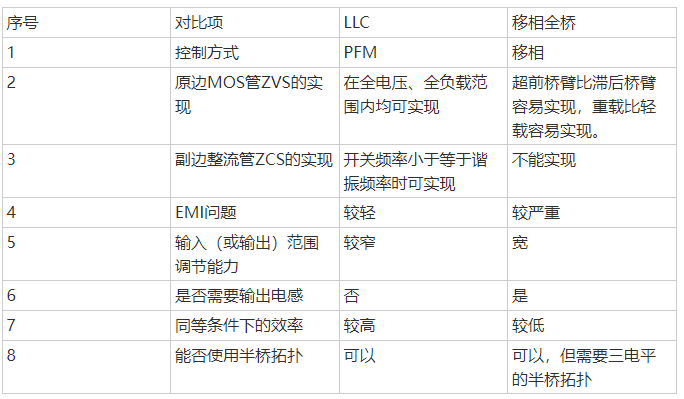

最后我們對比一下LLC和移相全橋的異同。

最后我們對比一下LLC和移相全橋的異同。

移相全橋仿真波形

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280