首先我們先了解什么是MOSFET?全稱是金屬氧化物半導體場效應管(Metal-Oxide-Semiconductor Field Effect Transistor)這是MOSFET的簡易符號,表示了三個端子:柵(G)、源(S)和漏(D)。 因為這種器件是對稱的,因而可以源漏互換。 大家都知道,在數字電路中,MOS管作為開關的作用時,柵極電壓VG是高電平,晶體管把源極和漏極連接在一起; 如果VG是低電平,則源漏斷開。

但是,這是數字電路需要研究的內容,在模擬電路中,知道這些還遠遠不夠。 我們還是要回答幾個問題:VG取多大的時候器件導通?

閾值電壓是多少?

當器件導通(斷開)的時候,源漏之間的電阻值是多大?

這個電阻和VDS之間的關系是怎樣的?

哪些因素可以限制器件的速度?

這些問題小編會在以后給大家解答。

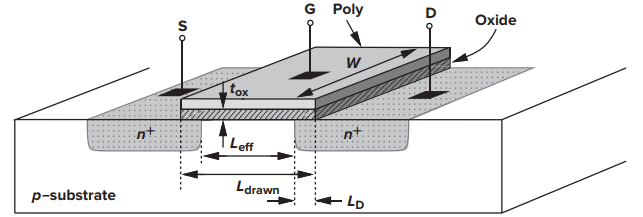

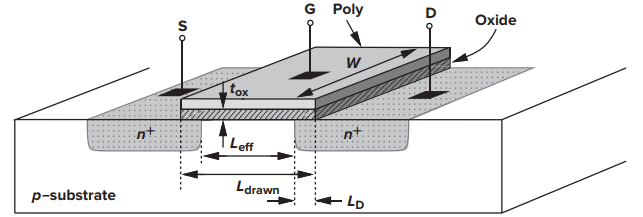

MOSFET的結構

圖為NMOS器件的簡易結構,器件制作在P型襯底上兩個重摻雜的n區形成源極和漏極。 重摻雜的多晶硅區(簡稱Poly)作為柵極。 一層氧化膜(Oxide)使柵和襯底分離。 Leff稱為有效柵長,Ldrawn稱為總長度。 LD是橫向擴散長度。 tox為氧化層的厚度。 Leff(有效柵長)和tox(氧化層厚度)對MOS電路的性能起著十分重要的作用。

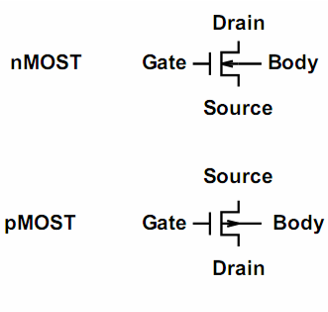

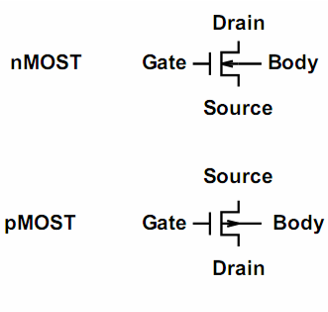

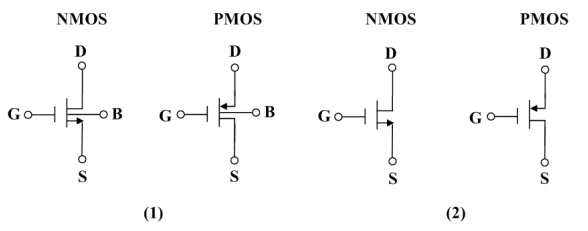

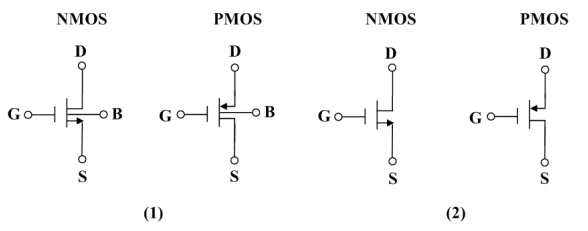

MOS的符號

NMOS管和PMOS管的電路符號所示,MOSFET是一個四端器件,襯底是第四端,用B表示。 由于在大多數電路中NMOS管和PMOS管的襯底分別接地和VDD。 所以我們在畫MOS管的符號時,經常省略這一連接。

閾值電壓

當柵極電壓VG從0開始上升時會發生什么情況呢?

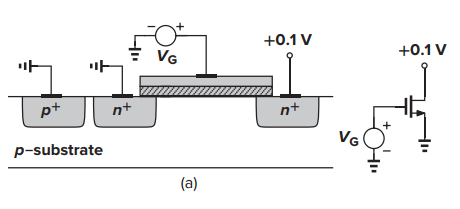

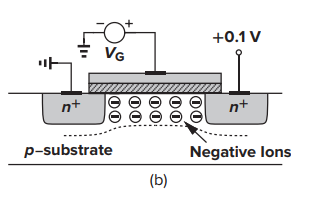

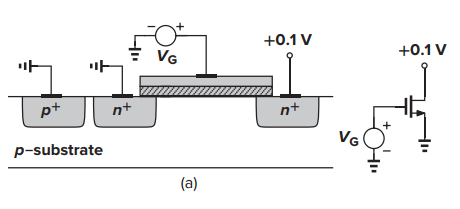

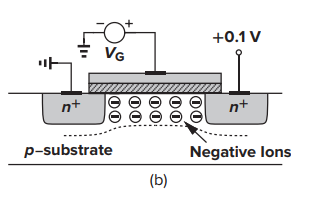

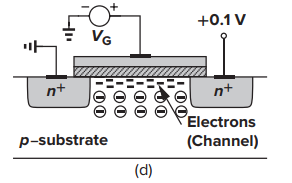

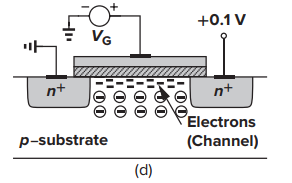

圖(a)所示的是一個NMOS器件,襯底接地。 當VGS等于0時; 兩個有源區被襯底分離,所以源漏之間沒有電流流動。 當VG逐漸升高時,在柵極和襯底之間的SiO2 絕緣層中產生了從柵極指向襯底的垂直電場EV。 在該電場作用下,襯底中的電子受到吸引,向襯底表面運動; 而襯底中的空穴受到排斥,向襯底內部運動。 向上運動的電子與表面的空穴復合,在表面層留下了不能移動的負離子,形成了一層耗盡層。 在這種情況下,沒有電流流動。 如圖(b)。

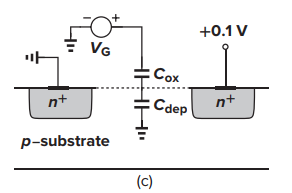

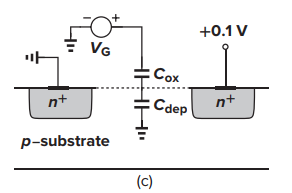

隨著VGS的升高,電場EV越來越強,表面層吸引的電子越來越多,產生的負離子也越來越多,耗盡層也越來越厚。 這樣的結構類似兩個電容串聯構成的分壓器,柵氧化層電容和耗盡層電容。 如圖(c)。

當VGS 上升到一定電位時,靠近表面的 P 型襯底發生變化,“反型”為與 N型材料類似的特性,因此該層稱為反型層。 反型層將漏極和源極兩個有源區連通,構成了源漏之間的導電溝道。 使晶體管產生反型層所需的VGS電壓稱為閾值電壓或開啟電壓,用Vth表示。

在器件制造過程中通常向溝道區注入雜質來調整閾值電壓,其實質是改變氧化層界面附近襯底的摻雜濃度。

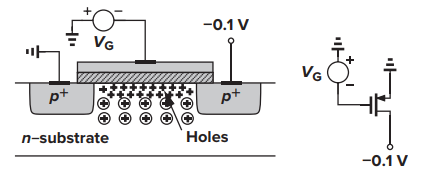

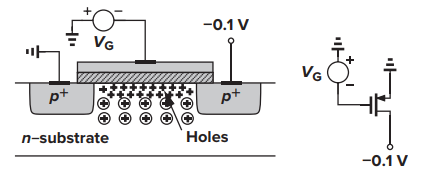

PMOS器件的導通現象類似于NFETs,但是其所有的極性都是相反的。 如圖,如果柵源電壓足夠”負“,在氧化層-硅的界面上就會形成一個由空穴組成的反型層,從而為源和漏之間提供了一個導電溝道。 因此,PMOS的閾值電壓通常是負值。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280