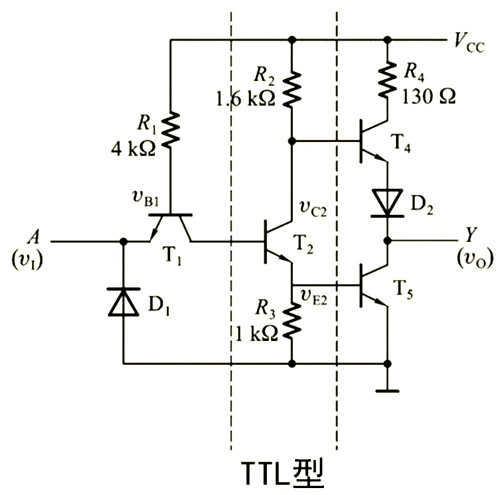

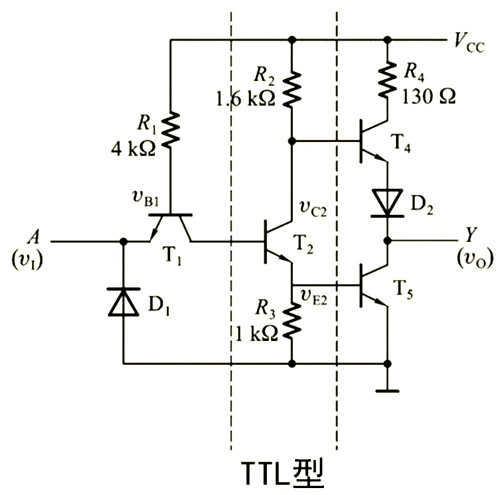

TTL電平

TTL電平信號在電路設計中被利用的最多是因為通常數據表示采用二進制規定,+5V等價于邏輯"1",0V等價于邏輯"0",這被稱做TTL(晶體管-晶體管邏輯電平)信號系統,這是計算機處理器控制的設備內部各部分之間通信的標準技術。

TTL集成電路的全名是晶體管-晶體管邏輯集成電路(Transistor-Transistor Logic),主要有54/74系列標準TTL、高速型TTL(H-TTL)、低功耗型TTL(L-TTL)、肖特基型TTL(S-TTL)、低功耗肖特基型TTL(LS-TTL)五個系列。

標準TTL:輸入高電平最小2V,輸出高電平最小2.4V,典型值3.4V,輸入低電平最大0.8V,輸出低電平最大0.4V,典型值0.2V。

肖特基型TTL(S-TTL):輸入高電平最小2V,輸出高電平最小Ⅰ類2.5V,Ⅱ、Ⅲ類2.7V,典型值3.4V,輸入低電平最大0.8V,輸出低電平最大0.5V。

低功耗肖特基型TTL(LS-TTL):輸入高電平最小2V,輸出高電平最小Ⅰ類2.5V,Ⅱ、Ⅲ類2.7V,典型值3.4V,輸入低電平最大Ⅰ類0.7V,Ⅱ、Ⅲ類0.8V,輸出低電平最大Ⅰ類0.4V,Ⅱ、Ⅲ類0.5V,典型值0.25V。

TTL優點:速度快

TTL缺點:無法大規模集成,因為三極管的靜態電流損耗很大,且TTL輸入只是雙極晶體管的基極,需要一些電流來打開它。輸入電流的大小取決于內部電路,最高可達1.6mA。當許多TTL輸入連接到一個TTL輸出時,這就成了一個問題,這通常只是一個上拉電阻或一個相當差的驅動高側晶體管。

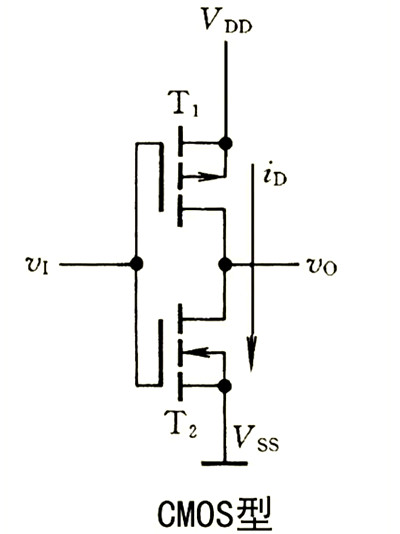

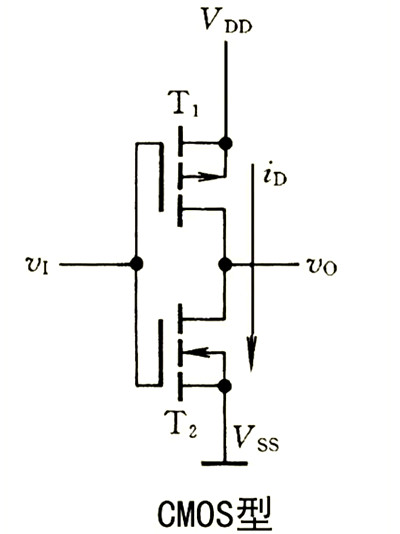

CMOS電平

COMS集成電路是互補對稱金屬氧化物半導體(Compiementary symmetry metal oxide semicoductor)集成電路的英文縮寫,電路的許多基本邏輯單元都是用增強型PMOS晶體管和增強型NMOS管按照互補對稱形式連接的,靜態功耗很小。

COMS電路的供電電壓VDD范圍比較廣在+5--+15V均能正常工作,電壓波動允許±10,當輸出電壓高于VDD-0.5V時為邏輯1,輸出電壓低于VSS+0.5V(VSS為數字地)為邏輯0。

CMOS優點:靜態電流幾乎為0,損耗小,靜態功耗接近為0,可在芯片里大規模集成。CMOS晶體管是場效應的,換句話說,柵極處存在的電場足以影響半導體通道進入導通。理論上,除了柵極的小漏電流外,不產生電流,漏電流通常在皮安培或納安培量級。

CMOS缺點:由于CMOS芯片有一定的輸入電容,因此上身時間有限,速度相對TTL較慢為了確保在高頻下上升時間快,CMOS需要一個大電流,在MHz或GHz頻率下可以達到幾安培的數量級。這個電流只有在輸入必須改變狀態時才被消耗,不像TTL,偏置電流必須與信號一起存在。

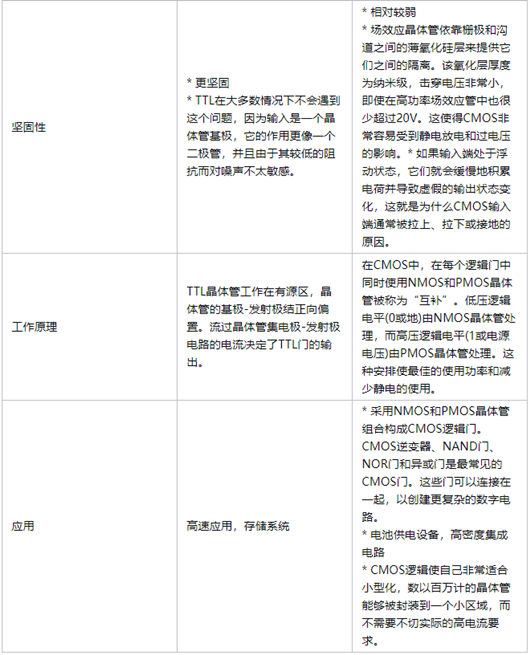

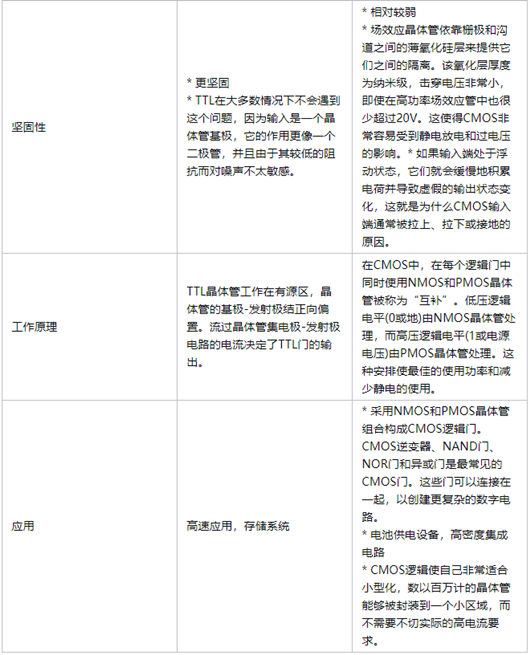

ttl與cmos的區別對比

1、CMOS是場效應管構成,TTL為雙極晶體管構成。

2、COMS的邏輯電平范圍比較大,一般在5V~15V,TTL只能在5V下工作。

3、CMOS的高低電平之間相差比較大、抗干擾性強,TTL則相差小,抗干擾能力差 。

4、CMOS功耗很小,TTL功耗較大,一般在1~5mA/門。

5、CMOS的工作頻率較TTL略低,但是高速CMOS速度與TTL差不多相當。

6、TTL電路是電流控制器件,而coms電路是電壓控制器件。

7、TTL電路的速度快,傳輸延遲時間短(5-10ns),但是功耗大。COMS電路的速度慢,傳輸延遲時間長(25-50ns),但功耗低。COMS電路本身的功耗與輸入信號的脈沖頻率有關,頻率越高,芯片集越熱,這是正常現象。

CMOS和TTL的共同之處

CMOS和TTL都不能讓輸入端口懸空。

因為端口懸空會導致意想不到的后果,比如受到噪聲干擾,增加功耗。

對于CMOS的輸入端,應該按照邏輯需求將他們要么和VCC連接,要么和GND連接。

對于TTL的輸入端,應該將他們和VCC連接,或者通過一個下拉電阻實現低電平。不能直接將TTL輸入端和GND直接連接,因為這樣會導致過電流,損壞器件。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280