lvds電平

LVDS :低電壓差分信號(Low-Voltage Differential Signaling)是一種信號傳輸模式的電平標準,LVDS傳輸支持速率一般在155Mbps(大約為77MHz)以上。它采用極低的電壓擺幅高速差動傳輸數據(采用CMOS 工藝的低電壓差分信號器件),實現點對點(或則點對多:M-LVDS)的連接,具有低功耗、低誤碼率、低串擾和低輻射等優點。

LVDS 器件的傳輸機制是把 TTL 邏輯電平轉換成低電壓差分信號,以便于高速傳輸。與傳統的 ECL邏輯相比,它采用 CMOS 工藝,其電壓擺幅更低(LVDS只有 400mV,ECL 為 800mv),動態功耗更小(輸出電流 3~5mA,只有 ECL 電路的 1/7),低 EMI,價格更低,因而在中等頻率(幾百M~幾GHz)差分信號應用上具有較大的優勢。

lvds電平標準

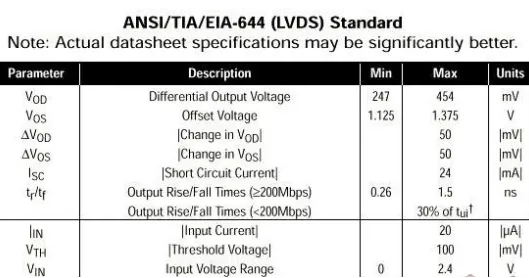

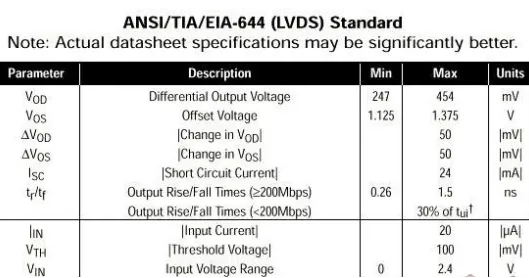

LVDS技術規范有兩個標準,即TIA(電訊工業聯盟)/EIA(電子工業聯盟)的ANSI/TIA/EIA-644標準(LVDS也稱為RS-644接口)與IEEE 1596.3標準。

標準參數的制定一方面取決于器件的制造工藝水平,另一方面取決于該標準面向的應用場景的性能要求。這意味著在不同的參數里,思考參數的取值的方法可能大相徑庭。

LVDS電路結構

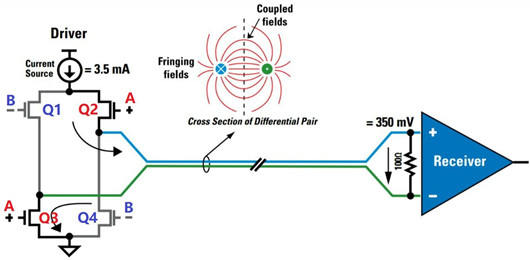

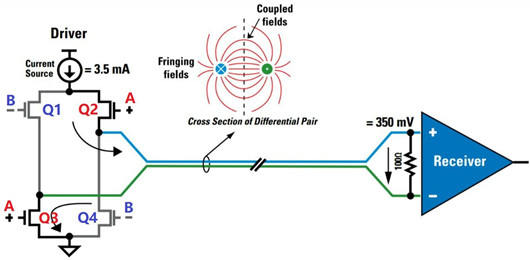

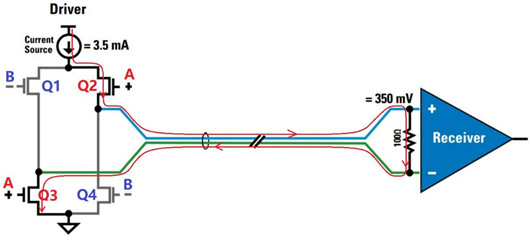

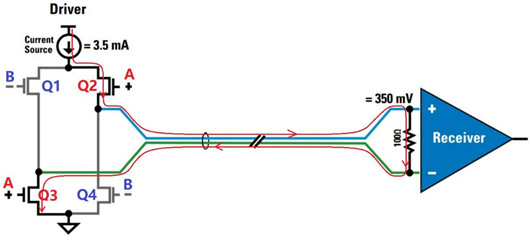

下圖為典型的LVDS電路,采用一對差分信號線傳輸數據;通過驅動3.5mA的穩定電流源,以350mV低振幅(100Ω終端匹配)的差動信號來高速傳送數據。其數據傳輸速度在規格內限定最大為655Mbit/秒,但這并不是極限值。通過各半導體廠商改進,可以實現3Gbit/秒左右的高速傳輸速度。

LVDS的輸出端驅動是一個3.5mA的電流源,并由兩組MOS管(4個)組成一對發送輸出;

當A+導通,B-斷開時:

1, 電流從右上角Q2(A+ MOS管)驅動出到藍色傳輸線,即右上A+ MOS管電流方向是:電流源(Driver)右上A+ MOS管藍色傳輸線100Ω終端電阻;

2, 左下角Q3(A+ MOS管)驅動接至GND,所以此時電流從綠色傳輸線通過左下角Q3流出到GND;左下A+ MOS管電流方向是:GND左下A+ MOS管綠色傳輸線100Ω終端電阻;

3, 整個電流通路最終電流在100Ω終端電阻側導通,并形成輸出電壓:3.5mA *100Ω = 350mV。

因為傳輸線提供的100Ω阻抗是交流阻抗,對于直流來說是傳輸線是高阻抗,所以終端必須有100Ω端接電阻來提供信號固定電平狀態下的回流,以保證輸出電壓;

需要再次強調的是:3.5mA電流從電源源流出到藍色傳輸線,和綠色傳輸線3.5mA電流流入GND,這兩者同時發生的,才能保證信號邊沿的同步;驅動電流的路徑并非是:電流源Q2藍色傳輸線100Ω終端電阻綠色傳輸線Q3GND。

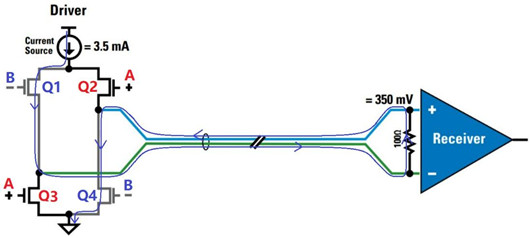

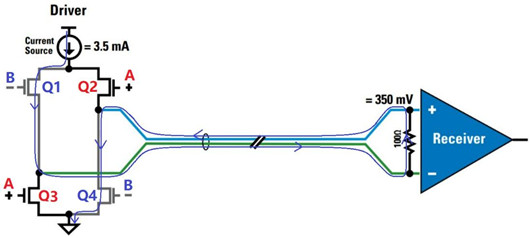

當B-導通,A+斷開時:

1, 此時3.5mA驅動電流從左上角Q1(B- MOS管)流出,并流入綠色傳輸線;

2, 同時藍色傳輸線電流流入右下角Q4(B- MOS管);

具體電流傳輸的方向,如上。

3, 電流通路最終電流還是在100Ω終端電阻側導通,但是電流方向與“A+導通,B-斷開”相反,并形成反向的輸出電壓:-3.5mA *100Ω = -350mV。

最終在輸出端形成 +350mV和-350mV信號擺幅的差分輸出。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280