積分電路 Integrator circuit

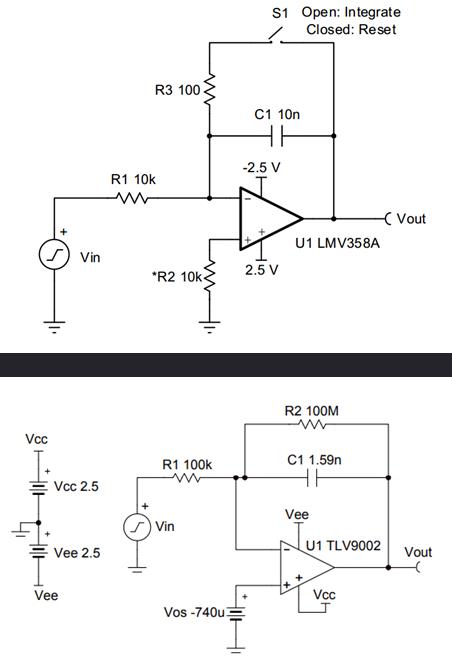

在運算放大器積分器電路中,電容器插入反饋環(huán)路中,并在反相輸入端與R1一起產生一個RC時間常數。

積分電路

積分器電路根據電路時間常數和放大器的帶寬,在一個頻率范圍內輸出輸入信號的積分。

輸入信號被施加到反相輸入,因此輸出相對于輸入信號的極性反相。理想的積分器電路將飽和到電源軌,具體取決于輸入失調電壓的極性并需要增加一個反饋電阻R2,以提供穩(wěn)定的直流工作點。反饋電阻器限制了執(zhí)行積分功能的較低頻率范圍。

設計須知

1.對于反饋電阻,請使用盡可能大的值。

2.選擇一個CMOS運算放大器,以最小化輸入偏置電流的誤差。

3.放大器的增益帶寬積(GBP)將設置積分器功能的上限頻率。

集成功能的有效性通常在距放大器帶寬約十年的時間開始降低。

4.需要將一個可調基準電壓連接到運算放大器的同相輸入,以消除輸入失調電壓,否則較大的DC噪聲增益將導致電路飽和。具有非常低的失調電壓的運算放大器可能不需要這樣做。

積分電路如下所示:

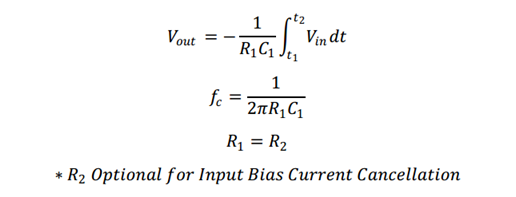

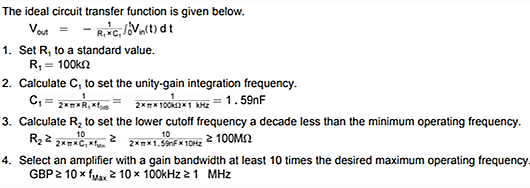

積分電路計算

積分電路輸出電壓Vout計算

如何設計

1、我們需要先設定電阻值,即就是上圖中的R1;

2、計算C1以設置單位增益積分頻率。

3、計算R2將下限截止頻率設置為比最小工作頻率低十倍。

4、選擇增益帶寬至少為所需最大工作頻率的10倍的放大器。

增益帶寬積

假設運算放大器的增益帶寬積為1 MHz,它意味著當頻率為1 Mhz時,器件的增益下降到單位增益。即此時A=1。同時說明這個放大器最高可以以1 MHz的頻率工作而不至于使輸入信號失真。由于增益與頻率的乘積是確定的,因此當同一器件需要得到10倍增益時,它最高只能夠以100 kHz的頻率工作。

單位增益帶寬

單位增益帶寬定義為,運放的閉環(huán)增益為1倍條件下,將一個頻率可變恒幅正弦小信號輸入到運放的輸入端,隨著輸入信號頻率不斷變大,輸出信號增益將不斷減小,當從運放的輸出端測得閉環(huán)電壓增益下降3db(或是相當于運放輸入信號的0.707)時,所對應的信號頻率乘以閉環(huán)放大倍數1所得的增益帶寬積。

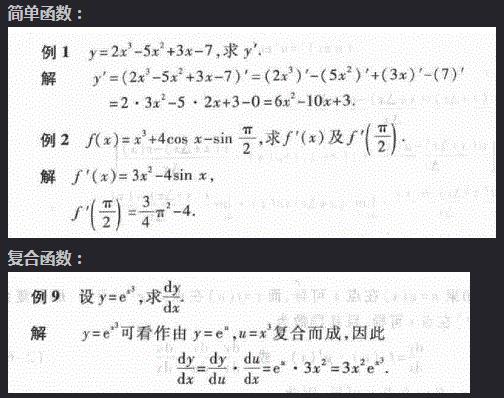

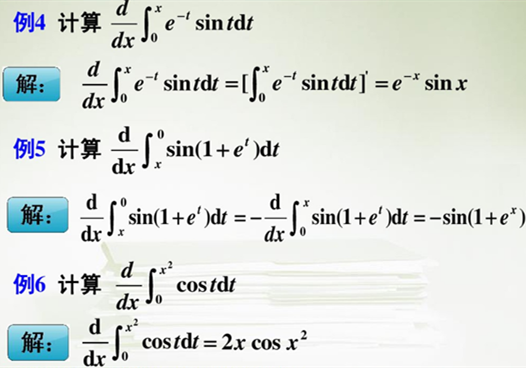

導數的運算

因為我們在高等數學里面是先講到的導數相關運算,再講述的是積分運算。

積分的運算

運放芯片本身需要注意的參數

VOS 輸入失調電壓

輸入失調電壓定義為集成運放輸出端電壓為零時。兩個輸入端之間所加的補償電壓。輸入失調電壓實際上反映了運放內部的電路對稱性。對稱性越好。輸入失調電壓越小。輸入失調電壓是運放的一個十分重要的指標,特別是精密運放或是用于直流放大時。輸入失調電壓與制造工藝有一定關系。當中雙極型工藝(即上述的標準硅工藝)的輸入失調電壓在±1~10mV之間。

IB 輸入偏置電流

運放兩個輸入端偏置電流的平均值, 確切地說是運算放大器工作在線性區(qū)時流入輸入端的平均電流。用于衡量差分放大對管輸入電流的大小。

IOS 輸入失調電流

在零輸入時,差分輸入級的差分對管基極電流之差,II0=|IB1-IB2|。用于表征差分級輸入電流不對稱的程度。通常,Ios為(0.5~5)nA,高質量的可低于 1nA。

AOL 開環(huán)電壓增益

開環(huán)電壓增益參數Aol被定義為輸出電壓的改變量與兩個輸入端之間電壓該變量之比。

運算放大器的靜態(tài)輸入指標及動態(tài)技術指標:輸入失調電壓、輸入失調電流、輸入偏置電流、共模抑制比、單位增益帶寬、轉換速率、壓擺率、輸入阻抗、輸出阻抗。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280