緩沖電路的設(shè)計方法

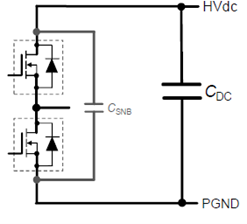

1.圖所示的緩沖電路是通過CSNB 吸收LTRACE 積蓄的能量。因此,在緩沖電路中形成的LSNB 必須比LTRACE 小。

由于CSNB 中積蓄的能量基本不放電,靜電容量越大電壓尖峰抑制效果變好,但使用的電容器的等價串聯(lián)電感 (ESL) 也必須考慮到LSNB 中。一般來說,電容器的尺寸越大ESL 越大,在選擇靜電容量時要注意。

為了將LTRACE 中積蓄的能量全部用CSNB 吸收, 需以算式(2)所示靜電電容為依據(jù)選定電容。

2.RC 緩沖電路的設(shè)計

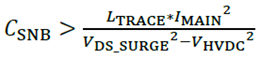

圖所示為RC緩沖電路動作時的電流路徑與CSNB緩沖電路一樣:

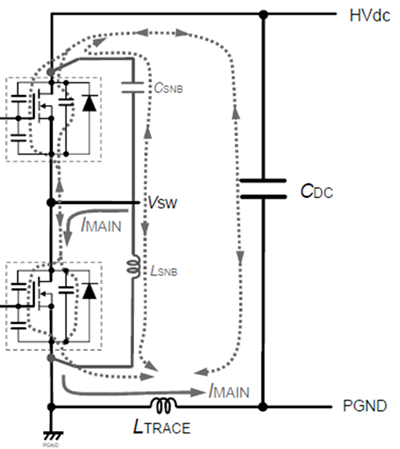

CSNB的數(shù)值由算式(2)決定,而RSNB 的參考值根據(jù)算式(3)求得。

fSW:開關(guān)頻率

VSNB:放電緩沖電壓(VDS_SURGE 的0.9 倍)

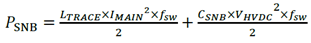

決定RSNB 之后,以算式(4)計算出RSNB 的消耗功率,選定功率滿足要求的電阻。

對于RC 緩沖電路,算式(4)追加了第二項,因為fSW 或VHVDC越高RSNB 所消耗的電力越大,PSNB 太大導(dǎo)致電阻選定困難時,必須降低CSNB 的靜電容量值重新計算。

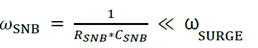

另外,為了RC 緩沖電路充分吸收電壓尖峰,RSNB 和CSNB 的諧振頻率ωSNB 必須比電壓尖峰的諧振頻率ωSURGE 低很多,需要結(jié)合算式(5)所示的RC 緩沖電路的諧振頻率ωSNB 來確認(rèn)。

3.放電型RCD 緩沖電路的設(shè)計

放電型RCD 緩沖電路的設(shè)計基本上與RC 緩沖電路相同。只是由于是通過二極管吸收的尖峰,所以不需要通過算式(5)確認(rèn)諧振頻率。并且,二極管必須選定為恢復(fù)電流小的型號。

4.非放電型RCD 緩沖電路的設(shè)計

非放電型RCD 緩沖電路與放電型RCD 緩沖電路不同,RSNB消耗的電力僅限于電壓尖峰的能量,用于抑制容許損失的RSNB的選擇范圍很廣。因此可以增大CSNB 的靜電容量,提高鉗位的效果。

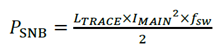

CSNB 由算式(2)決定,RSNB 由算式(3)決定,而RSNB 的消耗功率由算式(6)決定,沒有算式(4)中包含CSNB 及fsw 的第二項。

因此,由CSNB 或fsw 產(chǎn)生的消耗功率增加基本沒有,能選擇大的靜電容量的CSNB,不僅僅緩沖電路的鉗位效果更好,還能對應(yīng)fsw 的高頻化。

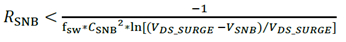

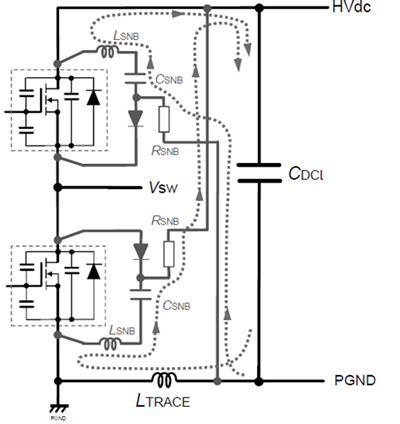

下圖所示為非放電型RCD 緩沖電路動作時的放電路徑。因為上臂的尖峰朝向PGND、下臂的尖峰朝向HVdc,放電流經(jīng)由RSNB 流動,不那么受線路電感影響。

另一方面,連接到MOSFET 的漏極源極之間的布線電感LSNB 因為電流變化大,電感值需要盡量小。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280