運(yùn)放失配設(shè)計(jì)

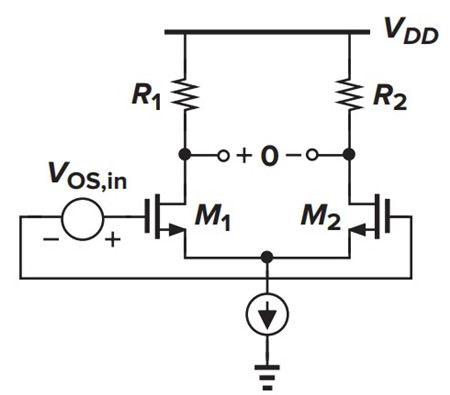

圖1 電阻負(fù)載運(yùn)放

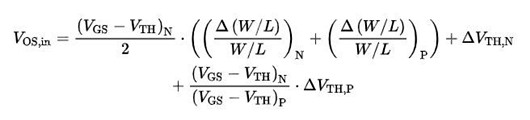

根據(jù)拉扎維《模擬CMOS集成電路設(shè)計(jì)》中14.2.1節(jié)的推導(dǎo),電阻負(fù)載的運(yùn)放的直流失調(diào)可以表示為式1:

由式(1)可知:

負(fù)載電阻失配與晶體管尺寸失配對失調(diào)電壓的影響隨著靜態(tài)工作點(diǎn)過驅(qū)動電壓增大而增大;

閾值電壓失配直接折合到輸入。

因此,在電路設(shè)計(jì)時(shí),應(yīng)該設(shè)計(jì)運(yùn)放的輸入對管具有更小的過驅(qū)動電壓以減小失調(diào)。

電流鏡失配設(shè)計(jì)

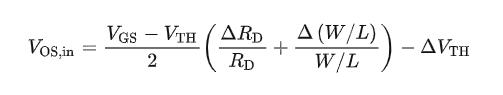

根據(jù)拉扎維《模擬CMOS集成電路設(shè)計(jì)》中14.2.1節(jié)的推導(dǎo),電流鏡的電流失配用平均電流值歸一化后可表示為式(2):

這個(gè)結(jié)果表示,為了使電流失配最小,必須使過驅(qū)動電壓達(dá)到最大,這與式(1)結(jié)論是相反的,這是因?yàn)樵谄椒铰晒街校S著VGS-VTH的增加,閾值電壓的失配對器件電流的影響越來越小。

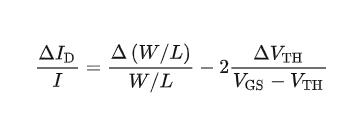

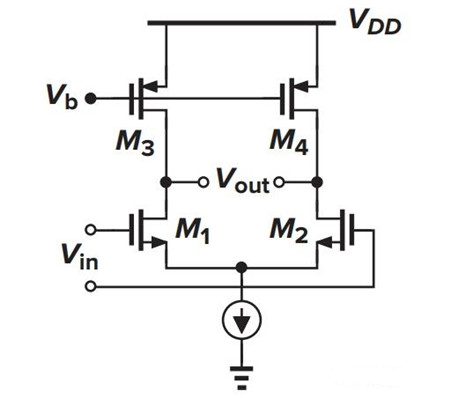

電流源負(fù)載的運(yùn)放失配設(shè)計(jì)

對于電流源負(fù)載的運(yùn)放,負(fù)載電流源會存在式(2)所示的的電流失配ΔID,其等效到運(yùn)放的失調(diào)電壓為ΔID/gm,對于給定的電流,gm=2ID/(VGS-VTH),即負(fù)載電流源的失配引起的運(yùn)放輸入失調(diào)會隨著輸入對管過驅(qū)動電壓的增大而增大。

圖2 電流鏡負(fù)載運(yùn)放

同時(shí)考慮運(yùn)放輸入對管和負(fù)載電流鏡晶體管的失配后,如圖2所示運(yùn)放的輸入失調(diào)電壓可表示為式(3):

式(3)可知,在設(shè)計(jì)運(yùn)放時(shí),在給定電流下,應(yīng)該使輸入對管具有更小的過驅(qū)動電壓,而使負(fù)載電流源晶體管具有更大的過驅(qū)動電壓,以此獲得更小的運(yùn)放輸入失調(diào)。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280