防浪涌抑制電路分析

電路原理

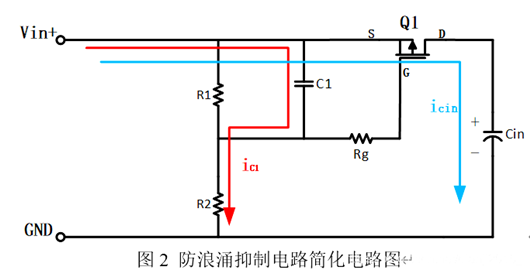

下圖是PMOS防浪涌電路的簡化原理圖。

首先說為什么采用PMOS,因?yàn)樨?fù)壓開通,可與輸入共地,若采用NMOS,可就需要charge bump才能導(dǎo)通了。

此電路的原理:

防浪涌抑制電路的基本原理是利用場效應(yīng)管的電流放大特性,控制輸入電流從0逐漸增加,緩慢的為輸出側(cè)電容充電,直至場效應(yīng)管完全導(dǎo)通,從而避免由于輸出側(cè)電容的瞬間短路特性導(dǎo)致產(chǎn)生的大電流。

工作過程主要分為三個(gè)階段,上電階段,C1充電階段,Cin充電階段。

1. 上電階段

上電瞬間,電容C1短路,PMOS管Q1的SG兩端電壓為0,Q1不導(dǎo)通,SD兩端阻抗無窮大,Cin上無電流。

2. C1充電階段

輸入給C1充電,充電時(shí)間常數(shù)約為R2*C1。隨著C1的充電,Q1的SG兩端電壓逐漸上升,當(dāng)達(dá)到PMOS管的開啟電壓Vth后,Q1導(dǎo)通。

3. Cin充電階段

隨著C1兩端電壓逐漸升高,Q1逐漸導(dǎo)通,管子上流過的電流逐漸增加,從而給Cin進(jìn)行充電,充電時(shí)間常數(shù)為Rsd*Cin,Rsd為Q1導(dǎo)通時(shí)的等效電阻。

當(dāng)C1兩端的電壓,達(dá)到R1兩端在輸入的分壓時(shí),充電結(jié)束。Cin兩端的電壓達(dá)到輸入電壓時(shí),充電結(jié)束。

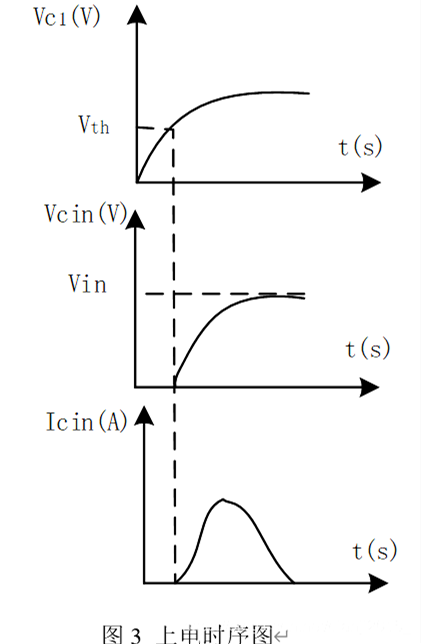

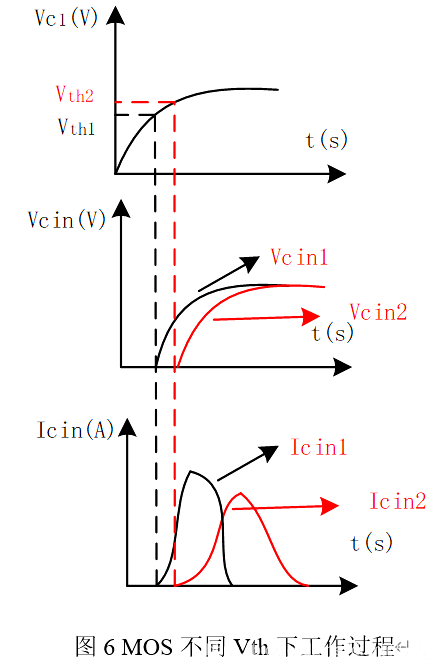

以上工作工程可由下圖表示。Vc1是C1兩端的電壓。Vcin是Cin兩端的電壓,Icin是Cin流過的電流。

我們來關(guān)注下電流的波形,為什么會(huì)這樣?從0增加到最大,斜率先增大,后減小,而后電流又快速下降。

我試圖想從公式上推導(dǎo),發(fā)現(xiàn)高階微分方程太難解出了,還是感性的說吧。

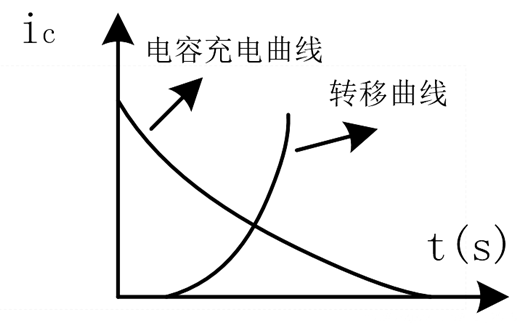

PMOS上的電流其實(shí)主要與兩條曲線有關(guān),一個(gè)是mos的轉(zhuǎn)移特性曲線,Vsg越大,-Id越大,那么電容充電電流的波形與轉(zhuǎn)移特性一致,另一方面若不考慮mos阻抗的變化,當(dāng)作常數(shù)R,那么隨著電容電壓增加,充電電流是越來越小的。

當(dāng)兩者達(dá)到一個(gè)平衡后,出現(xiàn)最大電流。不過電路中有寄生參數(shù),應(yīng)該不可能讓ic的電流不可導(dǎo),所以在極值點(diǎn)是平滑過渡的。

影響因素

RC參數(shù)的影響

要想電容充電電流小,充電慢,最簡單的來說就是增大時(shí)間常數(shù),包括mos管你都可以當(dāng)作阻抗來考慮,最開始阻抗無窮大,完全導(dǎo)通阻抗幾乎為0.

所以可以通過調(diào)節(jié)R2,C1可控制mos開啟電壓的上升速度,從而控制電流。當(dāng)然在調(diào)節(jié)R2時(shí),需同步調(diào)節(jié)R1,以確保電阻足夠的功率降額或者足夠的開啟電壓。

MOS參數(shù)的影響

實(shí)際上,PMOS參數(shù)的差異也會(huì)影響浪涌電流,比如轉(zhuǎn)移特性和Vth。

1)轉(zhuǎn)移特性的影響

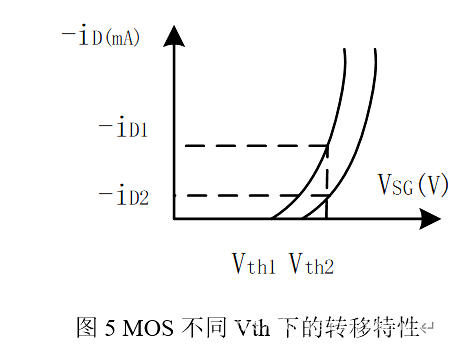

不同的轉(zhuǎn)移特性會(huì)導(dǎo)致相同的VSG下,導(dǎo)通電流的不同,如下圖所示。

2)Vth的影響

不同的Vth會(huì)導(dǎo)致MOS導(dǎo)通時(shí)電流的上升速率不同。假設(shè)MOS的電流放大倍數(shù)相同,即轉(zhuǎn)移特性曲線中斜率相同,Vth不同,導(dǎo)致相同VSG下,導(dǎo)通電流不同,Vth越小,導(dǎo)通電流越大。

MOS導(dǎo)通電流越大,Cin充電電流越大。而Cin總電荷量是一定的,由Q=CU=It可知,電流大,充電時(shí)間短,峰值電流大,而電流小,充電時(shí)間長,峰值電流小。

測試波形

結(jié)合實(shí)際浪涌電流波形進(jìn)行分析。上電一段時(shí)間后,回路電流快速上升,等效輸入電容充電,電流到達(dá)峰值后,由于電容電壓上升到一定值,充電電流減小,而后后級(jí)電路啟動(dòng),由于帶載,電容電壓被拉低,充電電流又會(huì)上升后回落,直到充電結(jié)束。

在電路參數(shù)不變的情況下,不同板卡測試結(jié)果不同,可能是由于MOS管差異導(dǎo)致,而MOS管的差異在實(shí)際應(yīng)用中很難保證,所以建議調(diào)整C1,R2,R1,如增大C1或R2,R1,可減小浪涌電流。由于整個(gè)電路啟動(dòng)時(shí)間的要求,RC不能太大,浪涌電流時(shí)間一般保證在2ms左右。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280