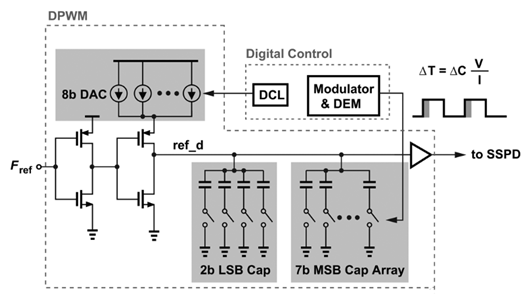

CMOS延時單元的設計,如下圖所示,8bitDAC和9bit電容陣列一起控制輸出脈沖的形狀,輸出信號的時鐘沿延時一般都是通過改變反相器的電流和輸出電容來改變的。

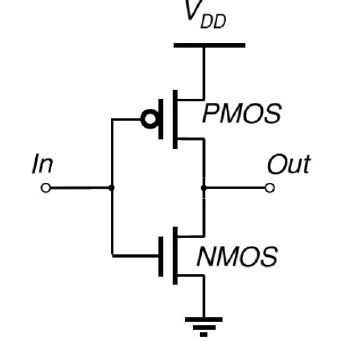

如下圖所示的反相器,其傳輸延時是由NMOS和PMOS的等效電阻對負載電容Cload(一般指下一級輸入電容)充放電所消耗的時間決定的。

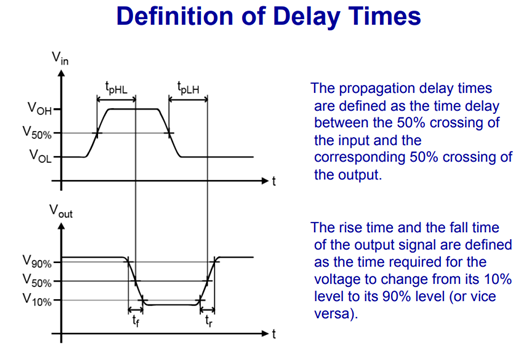

關于反相器中的一些延時定義如下:

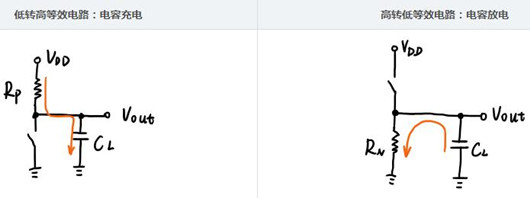

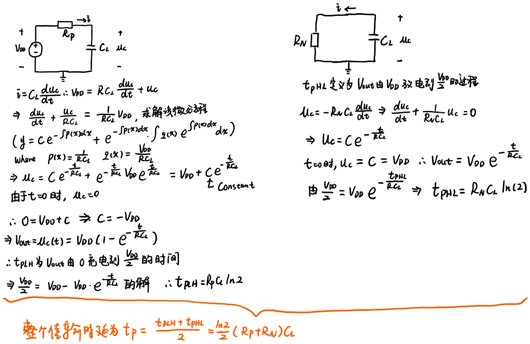

定義tpLH為Vout由低電平翻轉至高電平的傳輸延時(以50%為參考),此時的CMOS反相器可等效為下表左圖所示的電路。

定義tpHL為Vout由高電平至低電平翻轉的傳輸延時,此時的CMOS反相器可等效為下表右圖所示的電路。統稱為propagation delay。tf和tr分別表示下降延時和上升延時,這里暫時不作討論。

從電壓角度列方程,傳輸延時的推導如下:

從電流角度看的話,就直接是RC電流充放電了,可以直觀理解:電流越大,延時越小,電流越小,延時越大。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280