針對功耗來源,提出低功耗設計常用方法。

降低電源電壓;

減小負載電容;

減少MOS管數量;

減小連線電容

減少電荷分享的影響(對動態電路)

節點開關活動因子的影響;

從算法和體系結構角度優化;

選擇具有低功耗功能器件;

時鐘門控;

提高工藝

使用新型低功耗器件和材料,減少晶體管尺寸,如從28nm到16nm等。

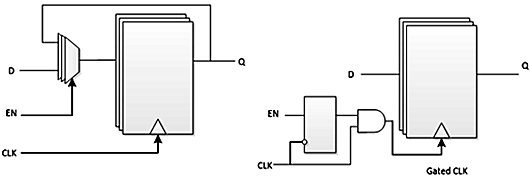

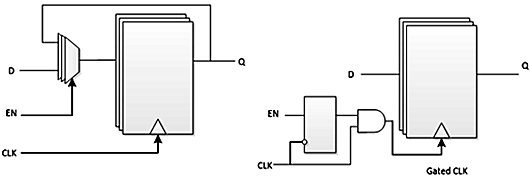

時鐘門控技術

頻繁的信號翻轉會造成很大的短路電流,以及對負載電容進行頻繁的充放電,即增大所謂的內部功耗(Internal Power)和切換功耗(Switch Power)。

在現代數字集成電路設計中,時鐘信號作為數據傳輸的基準,對于同步數字系統的功能、性能和穩定性起決定性的作用。

通常時鐘信號有高扇出,高頻率,路徑長的特點,在當前的高端SoC系統中,時鐘頻率已經超過1GHz,所以時鐘樹上消耗的功耗十分的可觀,大約占到系統總功耗的30%到40%。同時時鐘信號連接時序單元,如寄存器和鎖存器,所以這些時序單元上同樣消耗了不可忽視的動態功耗。

門控時鐘技術作為一項傳統的降低動態功耗的技術被廣泛應用于現代數字集成電路設計中,即用一個控制信號控制時鐘的開啟和關閉,在模塊不工作時關閉時鐘,在需要工作的時候,打開時鐘,從而通過降低觸發器總的翻轉率達到降低功耗的目的,其特點為實現簡單,并且十分有效。

通過用EN信號控制時鐘信號的開關,在EN信號無效時,寄存器的時鐘端將保持一個定值,D端的數值將不能傳到Q端。

多電壓域技術

芯片的動態功耗正比于電壓值的平方,靜態功耗正比于電壓值,因此芯片的電壓域管理策略對芯片的功耗影響很大。

多電壓域技術是按照芯片功能和應用需要,將不同的邏輯模塊放置在不同的電壓域中,這些電壓域由電源管理模塊分別獨立供電,使得不同的邏輯模塊可以在不同的電壓下工作。

例如,某一段時間內,某些性能要求不高的模塊可位于低電壓域中,而性能要求較高模塊的供電電壓相應較高,且多電壓域技術也是動態電壓頻率縮放(Dynamic Voltage and Frequency Scaling , DVFS)、靜態電壓縮放(Static Voltage Scaling, SVS)、自適應電壓縮放(Adaptive Voltage Scaling, AVS)設計的基礎。

電路采用多電壓域技術會給設計帶來一些的新的挑戰:

信號在不同電壓域之間傳遞,需要插入電平轉換器(Level Shifter)實現電平轉換。

由于芯片各個模塊會工作在多種電壓下,因此在各種電壓下的時序要求都要滿足,加大了靜態時序分析(Static Timing Analysis ,STA)的復雜度。

電源網格(Power grids)的布局規劃、模塊接口單元的電源布線等都變得更復雜。

板級上需要更多電壓調節器來提供各種不同電壓,增加板級設計的復雜度。

由于各個模塊電壓不同,模塊間上電/下電順序也需要仔細設計以避免電路出現死鎖。

電源門控技術

隨著工藝技術的發展,由漏電流所產生的功耗所占的總功耗比例越來越大。對于諸如手機的手持移動設備中的SoC芯片,休眠模式下漏電流功耗的大小是設計者在設計時必須考慮的設計因素。

對于希望在休眠模式下盡量節省功耗的設計來說,最好的辦法是,將處于休眠模式狀態的模塊的供電電源關斷而保持其它模塊的正常供電,這種技術叫電源門控技術。

電源門控技術與時鐘門控技術相比,時鐘門控降低的僅僅是電路的動態功耗,而電源門控不僅降低動態功耗,而且降低靜態功耗。

時鐘門控技術不影響設計電路的功能,也無須修改RTL(Register Transfer Level)代碼,它在設計和實現上可以是對設計者透明的,而電源門控技術影響各模塊之間的相互連接,安全進入和退出電源門控模式會增加很多額外的操作。

電源門控一般有兩種方法來實現:

外部電源門控(external power gating)。實現電源門控最基本的方法,適于消耗漏電功耗較少但關斷時間較長的設計。

舉個例子,一個SoC系統在板極上有CPU的專用電源,這個電源只提供電壓給CPU。外部電源門控技術就是,可以關閉這個電源以使CPU在非活動狀態時漏電功耗減小到零。但這種做法也需要最長的時間對電源門控的模塊進行供電和數據的重新加載。

內部電源門控(on-chip power gating)。內部電源門控是指在芯片內部用一些專門的邏輯單元如電源門控單元來控制所選模塊的供電情況。

外部電源門控技術與內部電源門控技術均能實現將電壓域中電壓關斷從而最大限度地減小漏電功耗的目的,但在物理實現過程中,內部電源門控技術要復雜得多。

器件低功耗

SOC系統中各個器件選型時,選擇具備低功耗功能器件,但器件無業務工作需求時,可以進入低功耗狀態。

RTL級優化

不同的RTL(RegisterTransferLevel,寄存器傳輸級)代碼,也會產生不同的功耗,而且RTL代碼的影響比軟件代碼產生的影響可能還要大。因為,RTL代碼最終會實現為電路。電路的風格和結構會對功耗產生相當重要的影響。

RTL級代碼優化主要包括:

①對于CPU來說,有效的標準功耗管理有睡眠模式和部分未工作模塊掉電。

②硬件結構的優化包括能降低工作電壓Vdd的并行處理、流水線處理以及二者的混合處理。

③降低寄存電容C的片內存儲器memory模塊劃分。

④降低活動因子a的信號門控、減少glitch(毛刺)的傳播長度、Glitch活動最小化、FSM(有限狀態機)狀態譯碼的優化等。

⑤由硬件實現的算法級的功耗優化有:流水線和并行處理、Retiming(時序重定)、Unfolding(程序或算法的展開)、Folding(程序或算法的折疊)等等基本方法以及其組合。

后端綜合與布線優化

SoC的功耗與寄生電容的充放電有很大的關系,作為后端綜合與布線,同樣也可采取一些措施來減少寄存器電容。能夠優化電路,減少操作(電路的操作),選擇節能的單元庫,修改信號的相關關系,再次綜合減少毛刺的產生概率。

實際上,這個部分與使用的工具相關。與軟件部分有相同之處,后端綜合與布線同軟件的編譯差不多。軟件編譯的結果是產生可執行的機器代碼;而RTL的綜合與布線是把RTL代碼編譯成真實的電路。

但是,后端綜合與布線優化比較編譯優化有更好的效果。這是因為一段RTL代碼所對應的電路是能夠有多種形式的;同時現有些編譯器會根據設計者提供的波形,智能地修改電路(前提是最終電路的效果還是一樣的),編譯器就會實行相關的優化。

但是后端綜合的優化與RTL級代碼優化和時鐘控制相比,同樣的RTL級與時鐘優化所產生的影響要遠大于用編譯工具所產生的影響。

功耗的精確計算

后端綜合與布線工具不但能夠根據基本單元提供的功耗參數實行優化,還能夠根據這些參數估算出整個SoC的功耗。正因為有這樣一些工具,使我們能夠精確地知道我們所設計的是否達到設計要求。

萬一設計功耗不符合總體要求,則可能要求從系統級到物理綜合布線都要做出檢查與分析,做出可能的改進,盡可能地減少功耗以達到設計要求。

自適應閾值電壓調節技術

自適應閾值電壓調節技術(Adaptive Voltage Scaling,AVS)技術的基本思想是將PVT因素對電路的影響歸為延時特性的變化,在電路中加入監測單元監測延時信息,根據電路延時調節電壓,降低設計階段預留的電壓余量,從而使芯片處于最佳能效狀態,降低功耗。

AVS技術利用硬件調節電壓,無需軟件執行,調節效率高且不影響系統性能;它可以降低工藝偏差、溫度及老化對芯片的影響,提高芯片的產量與質量,還可以降低芯片電源IR-drop的影響;另外它只需在SoC中添加少量監測電路即可實現,額外的面積及功耗消耗都不大。

AVS的監控單元有兩種常用的方法。

一種是環形振蕩器監控的方法,環形振蕩器的監控方法是在芯片中放置工作在相同環境(工藝、電壓、溫度相同)下的環形振蕩器,通過環形振蕩器的振蕩頻率可以知道在當前溫度、工藝環境下頻率與電壓的關系,從而達到對整個芯片的工作環境進行監控的目的。

另一種是關鍵路徑監控方法,通過可配置的延遲鏈來復制關鍵路徑,使可配置的延遲鏈的延遲長度和關鍵路徑相同,這些可配置的延遲鏈包含反相器、與非門和線延遲等等。一個典型的關鍵路徑監控示意圖如圖所示。其中時間數字轉換器(Time Digitizer),是通過傳輸門和觸發器組成的。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280