輸出電容造成的影響

論及此問題,輸出電容的兩種影響至關重要:對輸出電壓紋波的影響,以及在負載瞬變后對輸出電壓的影響。

首先,我們來看一看輸出電容這個詞。這些電容一般安裝在電源的輸出端。但是,許多電力負載(電力消耗對象),例如FPGA,都需要使用一定數量的輸入電容。

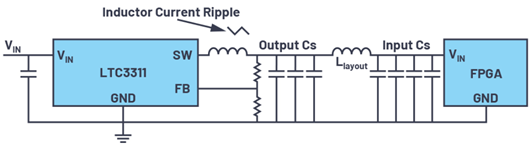

圖1顯示的是一種典型的包含負載和FPGA的電源設計。如果在電路板上,電壓生成電路和耗電電路之間的距離非常短,那么電源輸出電容和負載輸入電容之間的界限就會變得非常模糊。

通常需要利用某種物理分隔方法來加以區分,而這會導致產生大量寄生電感(Llayout)。

圖.開關穩壓器,包含所連接的FPGA對應的輸出電容和輸入電容

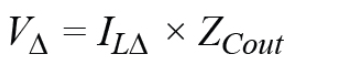

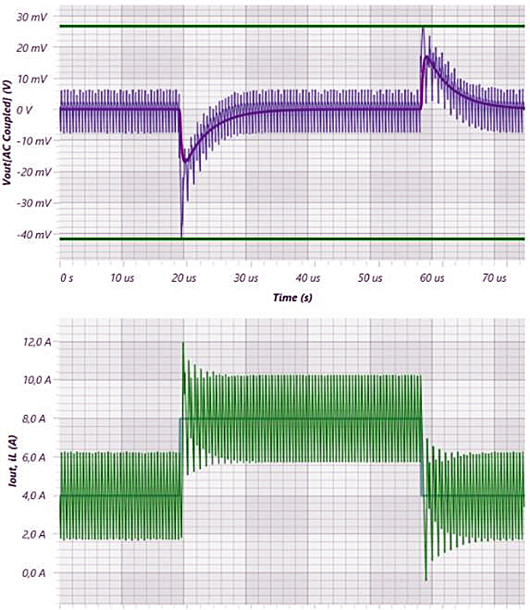

電源輸出端的電容形成決定了降壓型(降壓)開關穩壓器的電壓紋波。此時,經驗法則適用:輸出紋波電壓等于電感紋波電流 X 輸出電容的電阻。

這個電阻ZCout由電容的大小和數量,以及等效串聯電阻(ESR)和等效串聯電感(ESL)組成。如果電源輸出端只有一個電容,此公式高度適用。如果是更為復雜的情況(參見圖1),其中包含多個并聯電容,且因為布局(Llayout)的原因產生了串聯電感,那么計算不會如此簡單。

圖2.評估系統電源輸出端的不同電容

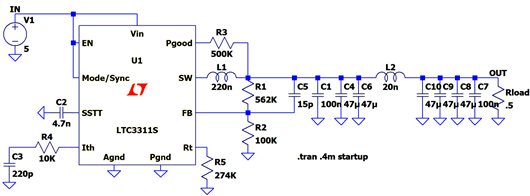

圖3.優化開關穩壓器的控制環路,以及減少輸出電容的數量

圖2所示為針對圖1提到的情況快速創建的電路圖。可以將不同值(包括ESR和ESL)設置給單個電容。也可以考慮板布局(例如Llayout)可能產生的影響。然后,會仿真開關穩壓器輸出端和負載輸入端的電壓紋波。

輸出電容也會影響負載瞬變后的輸出電壓失調。此時,特別需要注意的是,在某些限制范圍內,電源控制環路的控制速度和輸出電容的電感是相互關聯的。電源控制環路的速度如果更快,那么在負載瞬變之后,只需要更少數量的輸出電容即可保持在特定的輸出控制窗口之內。

最后但同樣重要的一點是,LTC3311-1具有自適應電壓定位(AVP)。AVP可以利用輸入誤差電壓預算并減少輸出電容器的數量,此外,設計人員還可以通過增加環路帶寬來實現減少輸出電容的數量。

AVP在低負載條件下稍微增大輸出電壓,在高負載條件下稍微降低輸出電壓。然后,如果發生負載瞬變,則更多動態輸出電壓偏差都發生在允許的輸出電壓范圍內。

建議找出哪些控制環路可以優化,以及可以減少多少個輸出電容。圖3所示為計算控制速度的截圖。其中顯示了在負載瞬變后計算得出的電壓過沖。可以通過改變輸出電容、調節開關穩壓器控制環路的速度來進行優化。

確定正確的參數后,即可減少電源中輸出電容的數量,如此可以節省資金和板空間,建議大家使用這個開發步驟。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280