在電路設(shè)計中,常見到利用 MOS 電容做去耦電容(也有利用來做miller補(bǔ)償?shù)碾娙荩虼藢?mosfet 的 c-v 特性曲線有必要進(jìn)行確認(rèn)。

關(guān)于具體的 c-v 曲線的仿真方法,首先可以從電容的定義(或者說特性)來確定測試方法,這也是 ee240 里面提到的仿真方法。

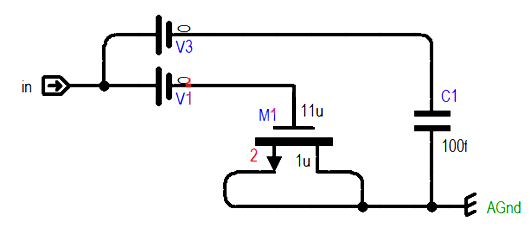

下圖是實現(xiàn) MOSFET C-V 曲線的仿真的具體電路(圖中加上的電容 C1 僅為方便比較)

在輸入節(jié)點(diǎn)加入一個電壓,做 AC 分析,同時掃描其 DC 值,考慮電容特性:ac 下 i/v=2*pi*f*C;如果令交流電壓 v ac=1,選擇頻率 2*pi*f=1,這時得到的交流電流大小就是電容值,相應(yīng)的 smart-spice 腳本如下:

vin in 0 ac 1

.ac DEC 10 '0.05/3.14159265' '0.5/3.14159265' sweep vin -2.5 2.5 0.05

.measure ac i_nmos find i(V1) at '0.5/3.14159265'

.measure ac i_cap find i(V3) at '0.5/3.14159265'

注:AC 分析似乎沒法對單獨(dú)的頻率點(diǎn)進(jìn)行分析,所以上面還是對一段頻率掃描,最后只取了我們所要的頻率點(diǎn)的結(jié)果。

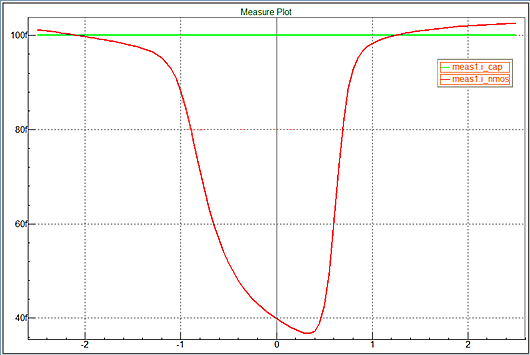

這樣得到的 C-V 曲線如下:

在 hspice 文檔里面提到了的另外的一種方法, 就是直接對上圖的 vin 做 dc 掃描, 利用 option dccap 使 spice 在 DC 分析時計算柵節(jié)點(diǎn)的所有電容, 得到的結(jié)果與上面 ac 分析的方法也是一致的, 其具體的 samrt-spice 腳本如下:

.option dccap

.dc vin -2.5 2.5 0.05

.probe @M1[cgtot]

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹