電感降壓原理

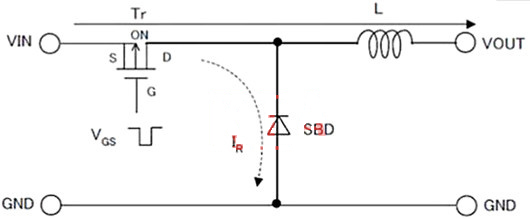

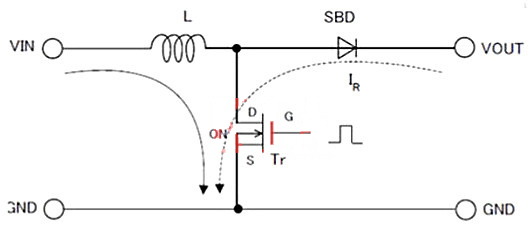

FET為ON時的電路圖

在FET為ON的時間里,L積蓄電流能的同時為輸出供電。虛線表示的電流路徑雖是微小的漏電流,但會使輕負載的效率變差。

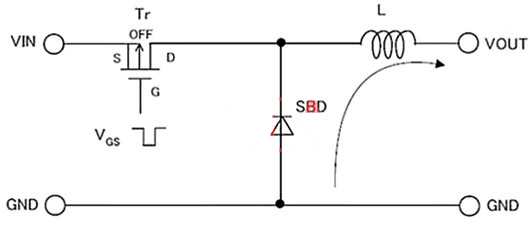

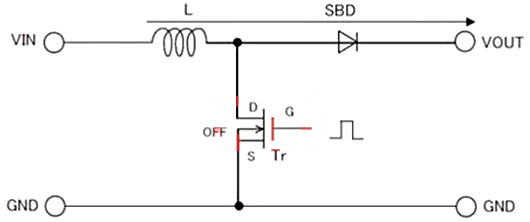

FET為OFF時的電路圖

在FET為OFF時,L要保持OFF前的電流值,使SBD為ON。此時,由于線圈的左端被強制性地降到0V以下,VOUT的電壓下降,即降壓電路原理。

由此,FET的ON時間長L里積蓄的電流能越大,越能獲得大功率電源,降壓的幅度越小。

降壓時,由于FET為ON時也要給輸出供電,所以不需要限制占空比的最大值。

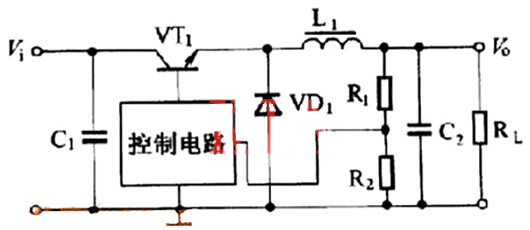

降壓式DC/DC 變換器基本工作原理電路如圖所示。VT1為開關管,當VT1導通時,輸入電壓Vi通過電感L1向負載RL供電,與此同時也向電容 C2充電。在這個過程中,電容C2 及電感L1中儲存能量。

當VT1截止時,由儲存在電感LI 中的能量繼續向RL供電,當輸出電壓要下降時,電容C2中的能量也向RL放電,維持輸出電壓不變。二極管VD1為續流二極管,以便構成電路回路。

輸出的電壓Vo經R1和R2 組成的分壓器分壓,把輸出電壓的信號反饋至控制電路,由控制電路來控制開關管的導通及截止時間,使輸出電壓保持不變。

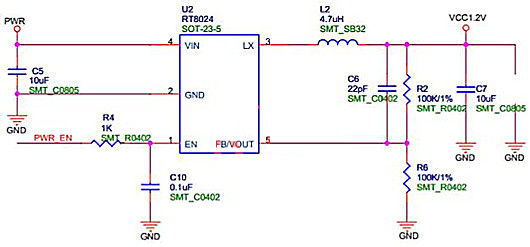

控制電路和VTI,VDI是一體的都是RT8024

電感升壓原理

FET為ON時的電路圖

在FET為ON的時間里在L積蓄電流能。虛線表示的電流路徑雖是微小的漏電流,但會使輕負載的效率變差。

FET為OFF時的電路圖

在FET為OFF時,L 要保持OFF前的電流值,相當于在輸入回路增加了一個“電源”。

由于線圈的左端被強制性固定于VIN,因此輸出VOUT的電壓要大于VIN, 即升壓電路原理。由此,FET的ON時間越長(FET的觸發占空比D越大),L里積蓄的電流能越大,越能獲得電源功率,于是升壓就越高。

但是,FET 的ON時間太長的話,給輸出側供電的時間就極為短暫,FET為ON時的損失也就增大,變換效率變差。因此,通常要限制占空比的最大值,不超過適宜的占空比D。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹