COOLMOS(超結MOS)

超結金氧半場效晶體管(Super Junction Metal-Oxide Semiconductor Field-Effect Transistor,SJ MOSFET)

SJ MOSFET的技術主要有兩種,其一為由英飛凌(Infineon)開發的多磊晶技術,藉由摻雜(doping)磊晶在磊晶層上形成島狀的摻雜區域,使該區域擴散形成一個氮摻雜(N-doped)平面。

另一種技術則采用深反應離子蝕刻挖出溝槽狀結構,再將氮摻雜材料填補于溝槽,制造出超接面的結構,開發此科技的業者主要為東芝(Toshiba),快捷半導體(Fairchild Semiconductor) 及艾斯摩斯科技(IceMOS Technology)。

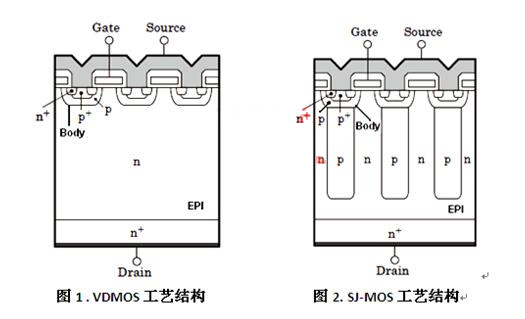

VDMOS與VDMOS的結構差異

為了克服傳統MOS導通電阻與擊穿電壓之間的矛盾,一些人在VDMOS基礎上提出了一種新型的理想器件結構,既我們所說的超結MOS,超結MOS的結構如圖2所示,其由一些列的P型和N型半導體薄層交替排列組成。

在截止態時,由于P型和N型層中的耗盡區電場產生相互補償效應,使P型和N型層的摻雜濃度可以做的很高而不會引起器件擊穿電壓的下降。

導通時,這種高濃度的摻雜可以使其導通電阻顯著下降,大約有兩個數量級。因為這種特殊的結構,使得超結MOS的性能優于傳統的VDMOS。

如下表中芯派電子的超結MOS與平面MOS部分參數比對可知,超結MOS器件參數優于平面MOS。

對于常規VDMOS器件結構, Rdson與BV這一對矛盾關系,要想提高BV,都是從減小EPI參雜濃度著手,但是外延層又是正向電流流通的通道,EPI參雜濃度減小了,電阻必然變大,Rdson就大了。

Rdson直接決定著MOSFET單體的損耗大小。所以對于普通VDMOS,兩者矛盾不可調和,這就是常規VDMOS的局限性。 但是對于超結MOS,這個矛盾就不那么明顯了。

通過設置一個深入EPI的的P區,大大提高了BV,同時對Rdson上不產生影響。

對于常規VDMOS,反向耐壓,主要靠的是N型EPI與body區界面的PN結,對于一個PN結,耐壓時主要靠的是耗盡區承受,耗盡區內的電場大小、耗盡區擴展的寬度的面積。

常規VDSMO,P body濃度要大于N EPI,大家也應該清楚,PN結耗盡區主要向低參雜一側擴散,所以此結構下,P body區域一側,耗盡區擴展很小,基本對承壓沒有多大貢獻,承壓主要是P body--N EPI在N型的一側區域,這個區域的電場強度是逐漸變化的,越是靠近PN結面,電場強度E越大。

對于COOLMOS結構,由于設置了相對P body濃度低一些的P region區域,所以P區一側的耗盡區會大大擴展,并且這個區域深入EPI中,造成了PN結兩側都能承受大的電壓,換句話說,就是把峰值電場Ec由靠近器件表面,向器件內部深入的區域移動了。

在原先傳統LDMOS的漂移區中,通過pn交替的結構來代替單一淡濃度摻雜的漂移區,LDMOS的漏端為高濃度摻雜的n+區域,它直接連接到pn交替的漂移區。

為了克服傳統MOS導通電阻與擊穿電壓之間的矛盾,一些人在VDMOS基礎上提出了一種新型的理想器件結構,既我們所說的超結MOS coolmos實現的工藝有很多種,可以采用DT 填充P型-EPI或者多次注入。

一般我們選擇一顆MOS 大致看以下幾個參數 BV Id Rds Vth Qg Pd等。

但是這幾個參數,只有Qg和Id是交流參數,其他都是靜態參數。而半導體這東西就是隨溫升變壞的。那動態參數,其實是變壞的。

25度的電流是100A,也許125度的時候,電流只有50A,所以選型的時候要以高溫下(老化房)的數據為準。那選好了電壓、電流,剩下就是看Coolmos的損耗了。

Coolmos露在表面的是Rdson 較低,只有平面管的1/3或者1/4,那MOS的導通損耗必然較之平面管要低不少。

MOS的另外一個損耗,開關損耗其實往往更加占主導。開關損耗在MOS里最直接體現的數值是Trr。這也是Coolmos最核心的參數。從coolmos的發展來看 C3 C6 CP CFD CFD2 都是在Trr上下功夫(C6除外,他是C3的Cost down)。

Coolmos在實際應用中,MOS前段的Rg驅動,一般對電阻要求會低很多。這也能降低損耗。

舉個例子,20N60C3 MOS前段的驅動電阻一般可做到15mohm以下,但是也不是越低越好,開關越高,EMI的問題就出來了。所以驅動電阻的選擇要綜合考慮,在EMI允許的情況下,盡量降低驅動電阻。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹