常用的ESD保護器件主要有Diode、Resistor、P/NMOS、BJT、SCR等,因其具有雪崩擊穿、雪崩與注入等特性,能夠瞬間進入低阻態,故具有良好的電流泄放能力,可以作為ESD防護器件。

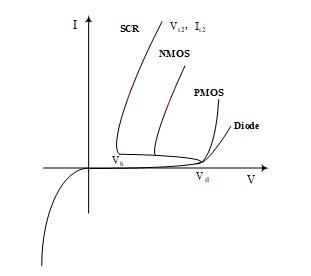

這類器件在電應力下的I-V特性示意圖見圖1。

圖1 常用ESD器件的I-V曲線示意圖

1. Diode

在ESD設計中,Diode是一種常見的器件。

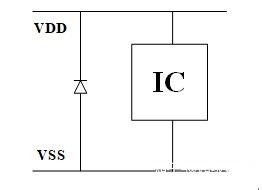

圖2為Diode的一種典型應用情況,在VDD相對于VSS發生Positive ESD Pulse時,Diode發生雪崩擊穿并釋放ESD電流,從而保護內部電路不受ESD影響。

但由于二極管完全通過雪崩擊穿釋放ESD電流,在大電流下器件的功耗很大,因此這種模式下二極管的抗ESD能力往往很低,器件的微分電阻也較大;

而在VDD相對于VSS發生Negative ESD Pulse時,該Diode為正偏并釋放ESD電流,由于二極管的正向導通電壓很小,此模式下器件的功耗很小,因此其抗ESD能力非常強。

圖2 Diode保護電路圖

由于Diode在正偏和反偏兩種狀態下的ESD能力差別非常大,因此目前在使用二極管作ESD保護器件時往往會采用非常大的器件面積提升二極管反偏狀態下的ESD能力,如此一來,缺點是非常明顯的,它增大了ESD器件的面積占用,更為嚴重的是,對于高頻引腳而言,此方式會帶來較大的寄生電容,使引腳的頻率特性變差。

2. MOS & BJT

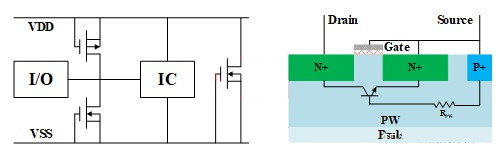

圖3 MOS器件作為ESD防護器件電路圖 圖4 GG-NMOS結構及等效線路圖

MOS與BJT用于ESD放電保護原理基本上是一樣的,均是通過寄生的BJT來釋放ESD電流。因CMOS使用最為廣泛的工藝之一,所以MOS器件成使用最為普遍的ESD保護器件。

采用MOS器件作為芯片的ESD防護架構示例如圖3所示。

為防止ESD器件在芯片正常工作時導通,MOS的柵極總是采用關斷的連接方式,即柵接地的NMOS(Gate-Grounded NMOS,GG-NMOS)和柵接電源的PMOS(Gate-VDD PMOS,GD-PMOS)。

GG-NMOS的等效電路如圖4所示,其ESD應力下的I-V曲線示意圖如圖1所示。

當漏端相對于源端發生Positive ESD Pulse時,漏端N+/Pwell結雪崩擊穿,擊穿產生的空穴電流將通過Pwell流至P+,并在Pwell的等效電阻Rpw上產生壓降,當該壓降大于寄生NPN器件的BE結正向導通電壓時,寄生的NPN器件即可導通,此時的電壓即為器件的觸發電壓Vt1,在此之后,由于寄生NPN器件的導通及其放大作用,使器件漏端電壓不需要很高的電壓即可維持大的電流,因此I-V曲線會出現折回(snapback)現象和負微分電阻現象,即在某段電流范圍內,器件兩端電壓隨著電流的增大反而減小。

當電流增大到某一值時,由于器件兩端的電壓不可能無限下降,以及器件內部的寄生電阻作用,負阻現象轉變為正阻,這一轉變過程中器件兩端的最低電壓即為器件的維持電壓Vh,它表征器件能將ESD Pulse鉗位的最低電壓。

在電流非常大時,器件內部產生的熱量將使器件內部由熱產生的載流子數遠大于雪崩擊穿和注入的載流子數,并且溫度越高,熱產生的載流子數量越大,進而形成正反饋,因此曲線會再次出現折回,該點的電壓和電流分別為器件的二次擊穿(熱擊穿)電壓Vt2和二次擊穿電流lt2,它們分別表征器件發生損毀時的電壓和器件最大耐受電流。

最終,器件將由于溫度過高而導致永久性損壞。而在漏端相對于源端發生Negative ESD Pulse時,電流可通過正偏的源端P+/Pwell/漏端N+二極管釋放。

與NMOS相比,PMOS通過體內寄生的PNP型BJT器件進行電流泄放,其電流放大系數遠低于NMOS中寄生的NPN型器件。

因此,如圖所示,PMOS器件可能沒有折回現象,考慮到器件的防護效率,PMOS的使用遠沒有NMOS普及,一般只作為電源VDD與I/O引腳之間的防護。

3. Resistor

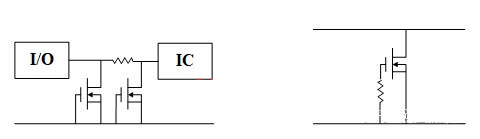

圖5 保護方案中的限流電阻 圖6 GG-NMOS結構中的柵極電阻

Resistor不單獨用于芯片的ESD保護,它往往用于輔助的ESD保護,如芯片Input第一級保護和第二級保護之間的限流電阻。

如圖5,當ESD電流過大,第一級ESD器件難以將電壓鉗位至安全區域時,第二級ESD器件的導通將使其與電阻分壓,從而進一步降低進入內部電路的電壓。

又如用于GG-NMOS的柵電阻,如圖6所示,NMOS的柵極通過一電阻接地,而非直接接地。

如此一來,在NMOS漏端發生正向的ESD脈沖時,由于NMOS的漏一柵電容,會使得器件的柵極耦合出一正的電勢,該電勢會促使NMOS的溝道開啟,從而起到降低NMOS在ESD應力下觸發電壓的目的。

4. SCR

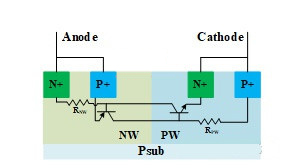

圖7 SCR結構及等效線路圖

SCR器件是除正向Diode外抗ESD能力最強的器件。

它的結構如圖7所示,當陽極出現Positive ESD Pulse時,Nwell/Pwell結發生雪崩擊穿,擊穿產生的電子電流和空穴電流分別流過電阻RNw和Rpw,使PNP器件和NPN器件開啟,陽極的P+注入大量空穴,陰極的N+注入大量電子,注入的空穴成為NPN器件的基極電流,注入的電子成為PNP器件的基極電流,正反饋過程得以形成,使Nwell和Pwell均出現強烈的電導調制效應,繼而降低器件兩端的壓降。

因此,SCR器件的維持電壓往往很低,并由此導致其抗ESD能力非常強,微分電阻也非常小。在陽極出現Negative ESD Pulse時,電流可通過正偏的陰極P+/陽極N+釋放。

由于這種SCR的觸發要靠Nwell和Pwell結的擊穿來實現,在CMOS工藝中,其擊穿電壓大約有幾十伏,遠高于一般器件的柵氧擊穿電壓,達不到ESD防護的效果。因此對于低壓CMOS芯片而言,SCR的觸發電壓需要通過一些方法降低,以滿足芯片的保護要求。

SCR的高It2使得器件可以以很小的寬度達到芯片的抗ESD要求,因此使用SCR器件可以有效的降低由ESD器件帶來的寄生電容,這一點對于RF芯片的ESD設計非常有利。

5. 各種器件的ESD性能比較

基于普及度較高的CMOS/BCD工藝,無論是低壓或者高壓應用來說,單位面積的ESD防護能力大致如下:SCR>MOS>Diode(反向擊穿)

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹