噪聲裕度和CMOS特性

在電氣工程領(lǐng)域,可以代數(shù)地將無噪聲的 壞情況下的輸入電平代數(shù)加到不引起輸出電壓偏離允許的邏輯電壓電平的外部信號(hào)的 電壓幅度稱為噪聲裕度。在通信系統(tǒng)工程領(lǐng)域,我們通常以分貝(dB)為單位測量噪聲容限。

此外,我們將噪聲容限定義為信號(hào)超過 可接受量的比率。關(guān)于數(shù)字電路,噪聲容限是信號(hào)超過產(chǎn)生“1”或“0”所需的閾值的量。

CMOS代表互補(bǔ)金屬氧化物半導(dǎo)體。其制造過程包括使用互補(bǔ)且對(duì)稱的p型和n型MOSFET對(duì)來實(shí)現(xiàn)邏輯功能。該技術(shù)正用于IC(集成電路)芯片,微控制器,CMOSBIOS,微處理器,存儲(chǔ)芯片和其他數(shù)字邏輯電路的構(gòu)造中。

我們還可以發(fā)現(xiàn)CMOS技術(shù)在諸如數(shù)據(jù)轉(zhuǎn)換器,RF電路,高度集成的收發(fā)器(通信)和圖像傳感器等模擬電路中的使用。總體而言,CMOS器件的兩個(gè)基本特征是低靜態(tài)功耗和高抗噪性。

由于一對(duì)MOSFET始終處于關(guān)斷狀態(tài),因此串聯(lián)組合僅在開關(guān)狀態(tài)(開和關(guān))時(shí)瞬間消耗大量功率。

結(jié)果,CMOS器件產(chǎn)生的熱量通常比其他形式的邏輯(例如TTL)產(chǎn)生的熱量少,即使它不改變狀態(tài),該邏輯通常也具有恒定電流。

CMOS反相器的特性

CMOS技術(shù)輕松集成到芯片邏輯和VLSI芯片中。此外,它們以較高的速度運(yùn)行,同時(shí)保持極少的功率損耗特性。此外,CMOS反相器提供了出色的邏輯緩沖功能,因?yàn)樗母吆偷驮肼暼菹尥戎匾?/div>

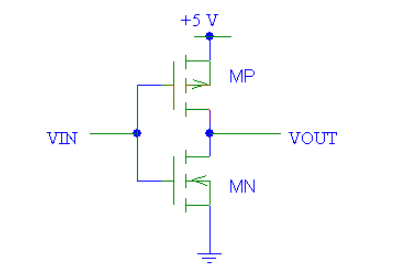

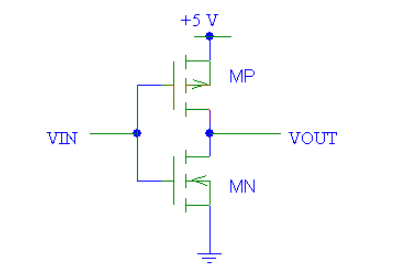

現(xiàn)在,讓我們仔細(xì)看一下CMOS反相器的工作原理及其特性。首先,CMOS反相器包含連接到漏極和柵極端子的PMOS(p型)和NMOS(n型)晶體管。

而且,它在PMOS源極端子上包含電源電壓(VDD),并在NMOS源極端子上包含接地。它具有到柵極端子的VIN連接和到漏極端子的VOUT連接。

請(qǐng)記住,CMOS反相器在其設(shè)計(jì)中沒有使用電阻,因此與標(biāo)準(zhǔn)電阻MOSFET反相器相比,它具有更高的功率效率。

參考上面的CMOS反相器圖,由于CMOS器件輸入端的電壓在5伏和0伏之間變化,因此PMOS和NMOS的狀態(tài)將相應(yīng)地不同。

因此,如果將每個(gè)晶體管建模為一個(gè)由VIN激活的簡單開關(guān),那么毫無疑問,我們可以看到CMOS反相器的功能。

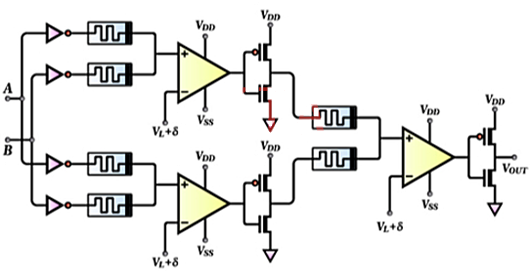

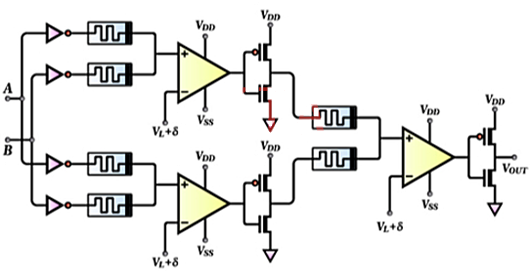

CMOS反相器中的噪聲裕度

現(xiàn)在,對(duì)于純數(shù)字反相器,由于存在一定程度的電容,它們不會(huì)立即從“1”(邏輯高)切換到“0”(邏輯低)。

當(dāng)逆變器從邏輯高電平過渡到邏輯低電平時(shí),會(huì)有一個(gè)不清楚的區(qū)域,在該區(qū)域中我們無法考慮電壓是低還是高。正是在這一時(shí)刻,我們認(rèn)為這是我們的噪聲余量。

我們必須考慮兩個(gè)噪聲容限,它們分別是:高噪聲容限(NMH)和低噪聲容限(NML)。

邏輯高電平的驅(qū)動(dòng)設(shè)備的電壓輸出(VOHmin)必須大于邏輯高電平的接收設(shè)備的電壓輸入(VIHmin)。

由于導(dǎo)線上存在噪聲,因此驅(qū)動(dòng)設(shè)備輸出端的邏輯高信號(hào)可能會(huì)以較低電壓到達(dá)接收設(shè)備的輸入端。

因此,邏輯高電平的噪聲容限NMH=(VOHmin–VIHmin)是您仍然可以正確接收邏輯高電平信號(hào)的容差范圍。

對(duì)于噪聲容限,我們可以說相同,對(duì)于邏輯低電平,NML=(VILmax–VOLmax),這規(guī)定了線路上邏輯低電平信號(hào)的容限范圍。噪聲容限越小,表明電路對(duì)噪聲越敏感。

噪聲容限是設(shè)計(jì)容限的標(biāo)準(zhǔn),可以在特定條件下建立適當(dāng)?shù)碾娐饭δ堋T肼曉纯梢园娫矗\(yùn)行環(huán)境,電場和磁場以及輻射波。晶體管的開關(guān)活動(dòng)也會(huì)產(chǎn)生不希望的噪聲。因此,為了在特定的噪聲條件下提供適當(dāng)?shù)木w管開關(guān),電路的設(shè)計(jì)必須包括這些特定的噪聲容限。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

- 上一篇:停電自鎖的電源開關(guān)電路圖解析

- 下一篇:三種晶體管接法比較解析

相關(guān)閱讀