閂鎖效應 (Latch Up) 是在器件的電源引腳和地之間產生低阻抗路徑的條件,這種低阻抗路徑可能會由于過大的電流水平而導致系統紊流或災難性損壞。本文介紹閂鎖效應產生的機理,并且介紹了3個電路設計的實用方法, 有效防止閂鎖問題。

如何避免線路中造成Latch-Up?

閂鎖效應 (Latch Up) 是在器件的電源引腳和地之間產生低阻抗路徑的條件。這種情況將由觸發事件(電流注入或過電壓)引起,但一旦觸發,即使觸發條件不再存在,低阻抗路徑仍然存在。

這種低阻抗路徑可能會由于過大的電流水平而導致系統紊流或災難性損壞。在設計電路應用時,需要確保應用于器件的電壓和電流水平符合絕對最大額定值要求。

在電路設計時, 可以考慮以下建議來防止閂鎖問題。

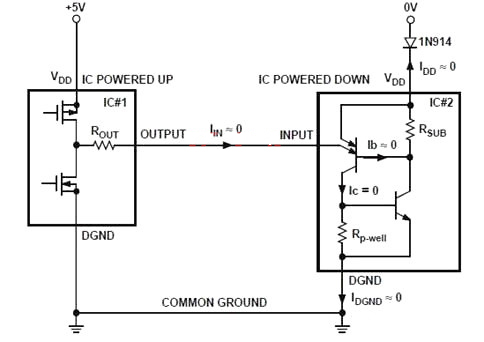

1. 如果由于上電排序而發生閂鎖,可以利用二極管與VDD串聯。

如果任何時候器件的數字輸入或輸出都超過VDD,可以在VDD串聯二極管(如下圖使用1N914)來阻止SCR觸發和隨后的閂鎖產生。這是因為二極管能夠防止寄生橫向PNP晶體管的基極電流從VDD引腳流出,從而防止SCR觸發。

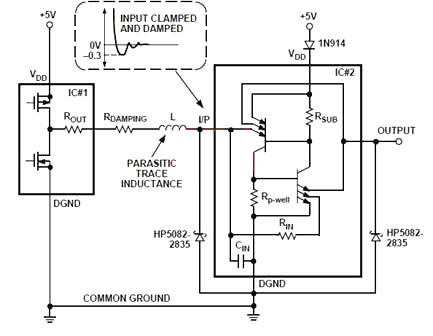

2. 將肖特基二極管添加到DGND(數字地)可防止電壓不足

如果器件的數字輸入和輸出隨時低于DGND,那么從這些輸入或輸出連接到DGND的肖特基二極管將有效地將負偏移鉗位在-0.3V至-0.4V之間。

這可以防止寄生NPN晶體管的發射極與基極結導通,并且還可以防止SCR觸發。

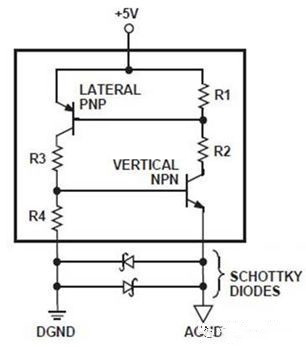

3. 在DGND和AGND (模擬地) 之間連接肖特基二極管

如果DGND電位偶爾會超過AGND 0.3V或更多,則可以在器件兩個引腳之間放置肖特基二極管來阻止相關寄生NPN晶體管的導通。

這提供了額外的防止閂鎖的保護。此外,前面提到的反向并聯連接的額外二極管可以在另一個方向上將DGND限制到AGND,這樣就大大減少了數字噪聲被注入器件的可能性。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹