所謂集成電路可靠性是指半導體集成電路在一定的工作條件下(指一定的溫度、濕度、機械振動、電壓等),在一定的時間內能夠完成規定作用的幾率。集成電路可靠性問題的提出是與電子信息產業迅速發展的下列三個特點分不開的。

1.電子信息系統產品的復雜程度不斷增長

電子信息系統產品復雜程度的重要標志是所需元件的數量越來越多。如美國轟炸機上的無線電設備情況是:1921年前飛機上還沒有無線電設備,1940年飛機上的電子設備只有一千多個,1950年B-47飛機上的電子設備發展到2萬多個,1955年B-52飛機上的電子設備發展到5萬多個,1960年B-58飛機上的電子設備發展到9萬多個;一般制導系統上的計算機部分就有10萬多個電子元器件。

一般來說,電子系統所采用的電子元器件個數越多,其可靠性問題就越嚴重,對于相關性很強的電子系統來說,其系統可靠性為所用電子元器件可靠性的乘積。假設元器件的可靠性均為99.5%,則采用100個元器件組成系統的可靠度僅為60%。若30萬個元器件組成系統,為了確保系統可靠度為95%,則要求每個元器件的可靠度為99.9999%以上。現代大型電子系統的電子元器件數量達百萬個以上,對電子元器件可靠性的要求則更高。

2.電子系統設備的使用環境日益嚴酷

現代電子系統設備的使用環境從實驗室到野外、從陸地到海洋、從高空到太空,還有使用在熱帶、南北極等地的。各種不同地方的電子設備需要經受不同的環境條件,如軍用武器裝備中的強振動和加速度、外部空間的粒子輻射和核武器的核輻射等。一般來說,使用條件越嚴酷,系統失效的可能性就越大,對可靠性的要求也越高。

3.電子系統的組裝密度不斷提高

為了減小電子系統的體積和重量,除了采用更高集成度的集成電路外,還需要采用多芯片組件(MCM)的方式進行二次集成。組裝密度的提高,使得系統內部的環境溫度迅速提高,加速電子元器件的老化過程,高速信號之間的串擾也越來越嚴重,所以對可靠性的要求也進一步提高。

一、集成電路可靠性

集成電路可靠性通常用失效率進行量度。瞬時失效率λ(t)定義為某個相當短的時間間隔Δt內,失效的器件數Nt與這段時間內工作的器件總數N(t)和時間間隔Δt的乘積之比,即

λ(t)=Nt/N(t)Δt

λ(t)采用非特(1非特=0.0001 %/1000小時=10^-9/小時)來度量。瞬時失效率簡稱為失效率,用于描述在各個時刻仍在正常工作的器件失效的可能性。

集成電路的可靠性效應可以分為6類:靜電效應、熱效應、二次擊穿效應、閂鎖效應、化學效應和輻射效應。

當帶有靜電荷的物體與非帶電導體接觸時,帶電導體會通過非帶電導體放電,即靜電放電。如果帶電體是通過集成電路進行放電,就會對器件帶來損傷,導致器件失效,即靜電效應。帶電人體對集成電路的靜電效應是最主要的。

集成電路工作時所消耗的功率要通過發熱的形式耗散出去,如果集成電路的散熱能力有限,則所消耗的功率會引起集成電路內部溫度的上升,如果集成電路的工作環境溫度過高或是由于在高寒地帶不連續工作等原因引起溫度交替變化,也會在集成電路內部產生高溫應力或溫度循環應力,從而引起集成電路失效,即熱效應。

二次擊穿是一種典型的集成電路體內失效,是嚴重威脅功率集成電路和高壓集成電路安全使用的主要失效模式。二次擊穿與雪崩擊穿有本質的區別,二次擊穿是不可逆的,具有破壞性,器件在二次擊穿狀態下停留時間過長或經受多次二次擊穿,其特性將顯著惡化,可能會被突然燒毀。

CMOS集成電路具有一種獨特的閂鎖(Latch Up)失效,不僅對其可靠性造成了嚴重威脅,而且成為進一步提高其集成度和性能指標的主要障礙。CMOS集成電路的基本邏輯單元是由一個PMOS晶體管和一個NMOS晶體管以互補形式連接構成。為了實現NMOS和PMOS的隔離,必須在n型襯底內加進一個p型區(稱為p阱)或者在p型襯底內加進一個n型區(稱為n阱)。由于NMOS和PMOS都做成增強型,所以通常在未接輸入信號時,它們都處于截止狀態,正電源端和負電源端之間幾乎沒有電流流過。但是,在測試和使用過程中,有時器件引出端(包括輸出端、輸入端和電源端等)受到外來的電壓或電流信號的觸發,正電源端和負電源端會出現很大的導通電流。該電流一旦開始流動、即使除去外來觸發信號也不會中斷,只有關斷電源或將電源電壓降到某個值以下才能解除這個電流。這個現象就是CMOS集成電路閂鎖效應。

集成電路在儲存、保管和使用過程中,特別是裝有器件的電子設備在沿海、海上和亞熱帶地區使用時,會遇到高溫潮濕、酸雨和鹽霧環境條件。在這種條件下,器件有可能因電化學反應遭到腐蝕而失效。一方面,器件的外引線和管殼可能直接被腐蝕,這種現象以柯伐合金引線最為顯著;另一方面,由于管殼的密封性缺陷或封裝材料本身的吸氣性(對塑料封裝),水汽可能會滲入管殼內部,使芯片表面的鋁金屬化布線被腐蝕或芯片電性能劣化,即化學效應。

隨著空間技術、核技術和戰略武器技術的發展,各種電子設備已經廣泛用于人造衛星、宇宙飛船、運載火箭、遠程導彈和核武器控制系統中。構成電子設備的電子元器件不可避免地要處于空間輻射和核輻射等強輻射應用環境之中,輻射作用會對元器件性能造成不同程度的破壞,進而使整個電子設備發生故障。例如,裝在導彈上的集成電路因受到輻照而失效,就會使彈上計算機系統發生邏輯誤差,結果使導彈失控而迷失方向或者過早爆炸,甚至不能爆炸,這種失效應被稱為輻射效應。

二、集成電路設計中提高可靠性的措施

集成電路的電路設計中提高可靠性的基本原則是把對器件的要求與具體工藝情況結合起來,因此熟悉工藝特點是搞好設計的基礎。在電路設計中可以采取以下一些措施來提高集成電路的可靠性:

(1)明確電路技術指標和使用環境。

(2)減小面積和復雜性。在滿足功能要求的基礎上簡化電路以盡量減少總面積和復雜性,減少接點數目(如減少雙極集成電路隔離島數目等)。面積減小能使缺陷減少,從而使可靠性提高。

(3)對于電路器件給予一定的容差,即按最壞情況進行設計,這也叫容差設計。

(4)在同樣參數指標情況下,盡量降低電路的功耗(例如工作電流要選擇恰當等),以降低電路工作時的結溫,提高可靠性;當最大電流Imax≤2×10^5A/cm2 時,還有利于防止電遷移。

(5)必要時要考慮元件的冗余設計,即增加并聯或串聯元件以確保可靠性,這一點常在部件或整機設計中考慮。

(6)在某些電路中加設保護電路,如集成穩壓器中加過壓保護、過流保護,集成運放輸出級加過流保護電路,在高溫度穩定的電路中加溫度補償電路,輸入端加輸入保護電路等。下面重點介紹CMOS集成電路中輸入端防靜電擊穿(ESD)的輸入保護網絡。

1.二極管和電阻雙層ESD保護結構

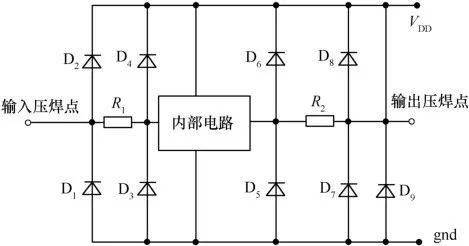

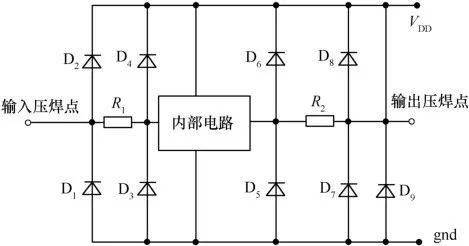

采用二極管和電阻雙層保護結構對ESD進行鉗位和濾除放電電荷是一種常用的保護電路技術,早期的NMOS電路都采用這種保護技術,目前的一些小規模CMOS電路也采用這種ESD結構。簡單的二極管在正偏時可以用來作為鉗位單元抑制ESD,其開啟電阻(Ron)比較低,約為10Ω,觸發電壓也比較低。另一方面,二極管在反偏時,其作為鉗位單元的特性較差,由于此時其Ron很高,約為100Ω,從而導致很大的能量消耗。這種ESD結構設計和工藝條件都比較簡單,是比較普遍的ESD保護電路的形式。對于有抗靜電要求的微米級CMOS集成電路,可以采用如圖1所示的保護電路,D2、D4、D6和D8是p+擴散電阻的分布二極管。D1、D3、D5、D7和D9是由p-n+結形成的二極管。

圖1 基本的二極管和電阻雙層ESD保護結構

利用二極管鉗位和RC低通濾波可以使端口處出現的ESD電荷脈沖通過保護網絡旁路,避免進入到電路內部,同時對端口處出現的其他干擾也能濾除。

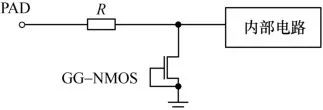

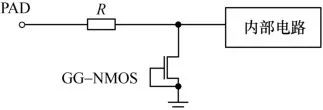

2.GG-NMOSESD保護結構

在CMOS集成電路技術中,GG-NMOS(柵、源、襯接地的NMOS)ESD保護結構是目前應用最廣泛的ESD保護措施,主要應用于微米及亞微米CMOS集成電路的ESD保護,圖2為典型的GG-NMOS ESD保護結構。GG-NMOS ESD保護結構是利用Snapback特性來鉗位瞬態高壓和分流,具有低鉗位電壓和低開啟電阻的特點,而二極管ESD保護結構的開啟電阻較大。當正脈沖(ESD)加在漏結上(n+/p),該結反偏,器件進入高阻抗狀態,直到達到擊穿電壓為止。由于處于高場狀態,在耗盡區產生電子、空穴對,電子被漏接觸電極收集,而空穴被襯底接觸電極所收集。相對于接地的源結,襯底的局部電勢不斷增加。當局部電勢增加到足以使源極—襯底結正偏時,電子就從源區注入漏區。

圖2 GG-NMOSESD保護結構

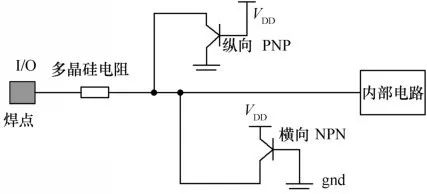

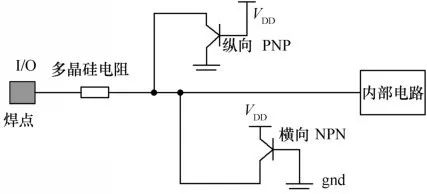

3.寄生PNP和NPNESD保護結構

全寄生的雙極性PNP和NPN晶體管ESD保護網絡,能有效避免PN結鉗位或MOS管鉗位結構產生的鉗位電流中的少數載流子向內部電路區擴散,其結構如圖3所示。

圖3 寄生PNP和NPN ESD保護結構

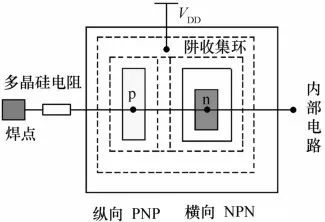

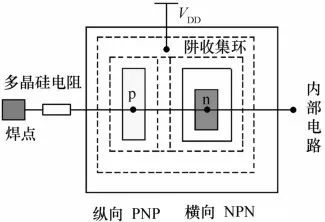

在這種ESD保護電路中,多晶硅電阻吸收了大部分的ESD能量。這種保護電路實際上是用p+和n+擴散區形成的,其鉗位方式是采用PN結鉗位的。由p+擴散區形成的二極管與n阱構成了寄生的垂直PNP晶體管。阱收集環包圍了n區和襯底,收集了大部分ESD放電注入襯底中的少數載流子,并且該環作為橫向NPN晶體管的集電極。該保護電路在靜電放電過程中,可以使到內部電路去的連線鉗位在VDD和VSS(地)電位之間。圖4是基于n阱CMOS工藝的寄生PNP和NPN ESD保護結構版圖。

圖4 基于n阱CMOS工藝的寄生PNP和NPN ESD保護結構版圖

4.SCRESD保護結構

采用寄生的橫向PNPN結構(SCR)的ESD保護結構是目前最有效使用最廣泛的一種ESD保護結構,具有大電流吸入/輸出、低的接通阻抗等特性,并具有較大的熱耗散體積。但是SCR器件需要有一個高觸發電壓,同時為了執行保護功能,該觸發電壓又必須小于輸入緩沖器或者輸出驅動器的損傷電壓。據實驗表明,在具有LDD和硅擴散1μm CMOS工藝制作的、陰陽極間距為6μm的寄生橫向SCR器件的觸發電壓為50V,所以不能采用單獨的寄生橫向SCR作為唯一的ESD保護器。為了提供更寬范圍的ESD保護,早期的SCR四層結構保護電路中,大都采用了諸如電阻和二極管等次級保護元件。也有研究者為了減少次級保護元件,采用兩種方法,降低寄生橫向的SCR觸發電壓。一種辦法是在橫向SCR內集成一個低擊穿電壓的短溝道NMOS晶體管,形成“LVTSCR”的結構,該結構的觸發電壓一般為10~15V,但是要將這個NMOS晶體管和橫向SCR結合在一起比較困難。另外一種解決辦法,為了獲得較低的觸發電壓而增加了一塊“NLCS”掩模,用來完成橫向SCR內深處的場注入。這種辦法得到的最小觸發電壓為9V。這個辦法的缺點是要增加掩模和工藝步驟,沒有廣泛應用。

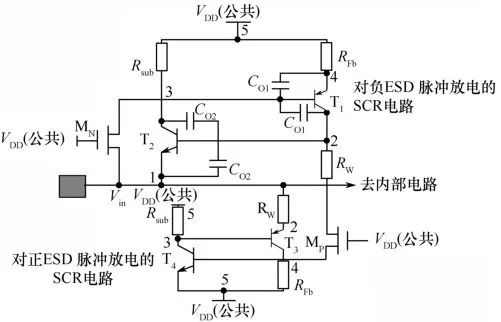

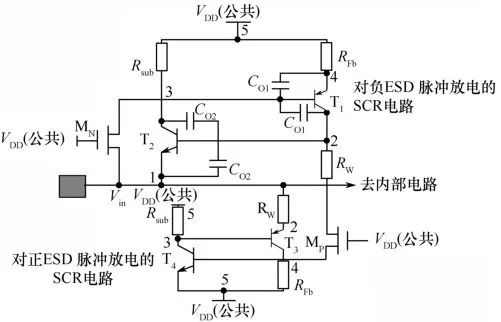

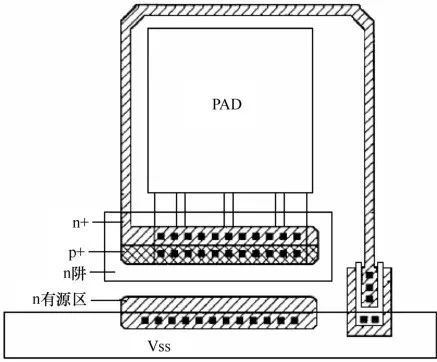

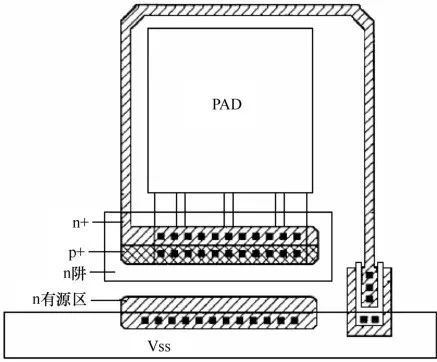

目前,雙寄生橫向SCR結構的ESD保護電路被廣泛采用,如圖5所示。在這個ESD保護電路中,一個寄生橫向SCR結構安排為對正的ESD脈沖放電,另一個則安排對負的ESD脈沖放電。兩個SCR都具有較低的觸發電壓。在這種ESD保護電路中,不存在PN結或器件的擊穿。這就避免了數次ESD瞬變之后,由于器件或結擊穿引起性能退化。這種保護電路具有小的版圖尺寸、低輸入電容和低接通電阻。比較理想的滿足了CMOS電路芯片上ESD保護電路的設計要求。圖6為其中一種SCRESD保護電路的版圖。

圖5 雙寄生橫向SCRESD保護結構

圖6 SCRESD保護結構版圖

三、集成電路的版圖設計中提高可靠性的措施

版圖設計的好壞直接影響電路生產的成品率及可靠性。好的設計不但本身很少帶來不可靠因素,而且對于工藝上難以避免的問題,也能預防或減弱其影響。

根據使用的溫度范圍(軍用-55~125℃,民用-25~85℃)及其他可靠性要求,版圖設計需要考慮電性能和熱性能。由電參數要求及工藝水平來確定元件的結構、尺寸,再考慮寄生效應、散熱等問題,從而最后確定整個電路的布局和布線。可靠性設計的內容很多,下面介紹一些主要措施。

1.關于金屬化層布線

大量的失效分析表明,因金屬化層(目前一般是Al層)通過針孔和襯底短路,且Al膜布線開路造成的失效不可忽視,所以必須在設計布線時采取預防措施。例如盡量減少Al條覆蓋面積,采用最短Al條,并盡量將Al條布在厚氧化層(厚氧化層寄生電容也小)上以減少針孔短路的可能。

防止Al條開路的主要方法是盡量少的通過氧化層臺階。如果必須跨過臺階,則采取減少臺階高度和坡度的辦法。

為防止Al條電流密度過大造成的電遷移失效,要求設計時通過Al條的電流密度J<2×10^5A/cm2,Al條要有一定的寬度和厚度。

對于多層金屬布線,版圖設計中布線層數及層與層之間通道應盡可能少。

2.版圖設計中的熱分布問題

據推測,芯片溫度每提高25℃失效率約增加一倍,所以要盡量降低芯片溫度以降低失效率。為防止結溫過高,功率較大的管子面積要設計得足夠大,而發射區有效邊長仍由最大電流確定。在整個芯片上發熱元件的布局分布要均勻,不使熱量過分集中在一角。在元件的布局上,還應將容易受溫度影響的元件遠離發熱元件布置。在必須匹配的電路中,可把對應的元件并排配置或軸對稱配置,以避免光刻錯位和擴散不勻。要注意電源線和地線的位置,這些布線不能太長。

3.其他措施

(1)元件尺寸的選擇要適當。應考慮功率密度、寄生效應、制版光刻誤差、橫向擴散及擴散容差等因素,Al條應覆蓋歐姆接觸孔并留一定余量。

(2)保證電路參數的要求:多發射極晶體管的長脖子區不宜太長,因為太長會導致fT下降;避免在輸出線上做擴散“地”道;外延層電阻島上接電源的歐姆接觸孔要擴n+。

此外,對于CMOS集成電路,為提高其抗閂鎖能力可在版圖設計上采取以下措施:①合理布置電源接觸孔,減小橫向電流密度和橫向電阻;②采用接襯底的環形VDD電源線(p阱),并盡可能將襯底背面接VDD;③增加電源VDD和VSS(GND)接觸孔,并加大接觸面積;④對每一個接VDD的孔都要在相鄰的阱中配以對應的VSS(GND)接觸孔,以便增加并行的電流通路;⑤盡量使VDD和VSS的接觸孔的長邊相互平行;⑥接VDD的孔盡可能安排得離阱遠一些;⑦接VSS的孔要盡可能安排在p阱的所有邊上。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹