CPLD (Complex Programmable Logic Device)直譯的話稱為復雜可編程邏輯芯片,是從PAL和GAL器件發展出來的器件,相對而言規模大,結構復雜,屬于大規模集成電路范圍。適合控制密集型數字型數字系統設計,其時延控制方便。CPLD是目前集成電路中發展最快的器件之一。

1.特點

CPLD具有編程靈活、集成度高、設計開發周期短、適用范圍寬、開發工具先進、設計制造成本低、對設計者的硬件經驗要求低、標準產品無需測試、保密性強、價格大眾化等特點,可實現較大規模的電路設計,因此被廣泛應用于產品的原型設計和產品生產(一般在10,000件以下)之中。幾乎所有應用中小規模通用數字集成電路的場合均可應用CPLD器件。CPLD器件已成為電子產品不可缺少的組成部分,它的設計和應用成為電子工程師必備的一種技能。

CPLD

2.組成

復雜的可編程邏輯器件CPLD規模大,結構復雜,屬于大規模集成電路范圍。

CPLD有五個主要部分:邏輯陣列塊、宏單元、擴展乘積項、可編程連線陣列和I/O控制塊。

2.1邏輯陣列塊(LAB)

一個邏輯陣列塊由16個宏單元的陣列組成,多個LAB通過可編程陣列(PIA)和全局總線連接在一起。全局總線從所有的專用輸入、I/O引腳和宏單元饋入信號。對于每個LAB有下列輸入信號。

來自作為通用邏輯輸入的PIA的36個信號

全局控制信號,用于寄存器輔助功能

從I/O引腳到寄存器的直接輸入通道

2.2宏單元

MAX7000系列中的宏單元由3個功能塊組成:邏輯陣列、乘積項選擇矩陣和可編程寄存器。各部分可以被獨自配置為時序邏輯和組合邏輯工作方式。其中邏輯陣列實現組合邏輯,可以為每個宏單元提供5個乘積項。乘積項選擇矩陣分配這些乘積項作為到“或門”和“異或門”的主要邏輯輸入,以實現組合邏輯函數,或者把這些乘積項作為宏單元中寄存器的輔助輸入:如清零、置位、時鐘和時鐘使能控制。

每個宏單元中的觸發器可以單獨地編程為具有可編程時鐘控制的D、T、JK或RS觸發器的工作方式。觸發器的時鐘、清零輸入可以通過編程選擇使用專用的全局清零和全局時鐘,或使用內部邏輯(乘積項邏輯陣列)產生的時鐘和清零。觸發器也支持異步清零和異步置位功能,乘積項選擇矩陣分配乘積項來控制這些操作。如果不需要觸發器,也可以將此觸發器旁路,信號直接輸給PIA或輸出到I/O引腳,以實現組合邏輯工作方式。

2.3擴展乘積項

每個宏單元的一個乘積項可以反相回送到邏輯陣列。這個“可共享”的乘積項能夠連到同一個LAB中的任何其它乘積項上。盡管大多數邏輯函數能夠用每個宏單元中的5個乘積項實現,但在某些復雜的邏輯函數中需要附加乘積項。為提供所需的邏輯資源,可以利用另一個宏單元,MAX70000結構也允許利用共享和并聯擴展乘積項,這兩種擴展項可作為附加的乘積項直接送到本LAB的任意宏單元中。利用擴展項可保證在實現邏輯綜合時,用盡可能少的邏輯資源實現盡可能快的工作速度。

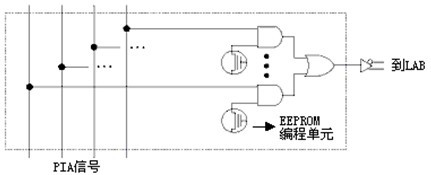

2.4可編程連線陣列PIA

通過可編程連線陣列可將各LAB相互連接構成所需的邏輯。這個全局總線是可編程的通道,它能把器件中任何信號源連到其目的地。所有MAX7000系列器件的專用輸入、I/O引腳和宏單元輸出均饋送到PIA,PIA可把這些信號送到整個器件內的各個地方。只有每個LAB所需的信號才真正給它布置從PIA到該LAB的連線,如圖是PIA信號布線到LAB的方式。

PIA信號布線到LAB的方式

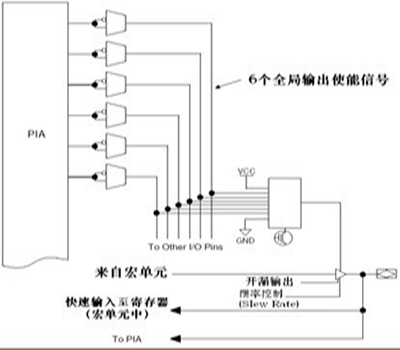

2.5I/O控制塊

I/O控制塊允許每個I/O引腳單獨地配置成輸入/輸出和雙向工作方式。所有I/O引腳都有一個三態緩沖器,它能由全局輸出使能信號中的一個控制,或者把使能端直接連接到地(GND)或電源(VCC)上。MAX7000系列器件的I/O控制框圖如圖所示。MAX7000器件有6個全局輸出使能信號,它們可以由以下信號驅動:兩個輸出使能信號、一個I/O引腳的集合、一個I/O宏單元的集合,或者是它“反相”后的信號。

I O控制框圖

當三態緩沖器的控制端接地(GND)時,其輸出為高阻態,而且I/O引腳可作為專用輸入引腳。當三態緩沖器的控制端接電源(VCC)時,輸出使能有效。

MAX7000結構提供了雙I/O反饋,且宏單元和引腳的反饋是相互獨立的。當I/O引腳配置成輸入時,有關的宏單元可以用于隱含邏輯。

3.優勢

(1)用CPLD來開發數字電路,可以大大縮短設計時間,減少PCB面積,提高系統的可靠性。

(2)CPLD還可以做數字IC設計的前端驗證,用這種方式可以很大程度上降低IC設計的成本。

(3)CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。

(4)CPLD如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法,或是硬件描述語言自由的設計一個數字系統。通過軟件仿真,我們可以事先驗證設計的正確性。在PCB完成以后,還可以利用CPLD的在線修改能力,隨時修改設計而不必改動硬件電路。

4.使用方法

CPLD是一種用戶根據各自需要而自行構造邏輯功能的數字集成電路。其基本設計方法是借助集成開發軟件平臺,用原理圖、硬件描述語言等方法,生成相應的目標文件,通過下載電纜(“在系統”編程)將代碼傳送到目標芯片中,實現設計的數字系統。這里以搶答器為例講一下它的設計(裝修)過程,即芯片的設計流程。

CPLD的工作大部分是在電腦上完成的。打開集成開發軟件(Altera公司 Max+pluxII)→畫原理圖、寫硬件描述語言(VHDL,Verilog)→編譯→給出邏輯電路的輸入激勵信號,進行仿真,查看邏輯輸出結果是否正確→進行管腳輸入、輸出鎖定(7128的64個輸入、輸出管腳可根據需要設定)→生成代碼→通過下載電纜將代碼傳送并存儲在CPLD芯片中。7128這塊芯片各管腳已引出,將數碼管、搶答開關、指示燈、蜂鳴器通過導線分別接到芯片板上,通電測試,當搶答開關按下,對應位的指示燈應當亮,答對以后,裁判給加分后,看此時數碼顯示加分結果是否正確,如發現有問題,可重新修改原理圖或硬件描述語言,完善設計。設計好后,如批量生產,可直接復制其他CPLD芯片,即寫入代碼即可。如果要對芯片進行其它設計,比如進行交通燈設計,要重新畫原理圖、或寫硬件描述語言,重復以上工作過程,完成設計。這種修改設計相當于將房屋進行了重新裝修,這種裝修對CPLD來說可進行上萬次。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹