如今,片上系統(SoC)技術的出現在數字系統設計引起變動;為適應產品盡快上市的要求,設計者必須合理選擇各EDA廠家提供的加速設計的工具軟件,以使其產品在本領域良性發展。而FPGA設計是當前數字系統設計領域中的重要方式之一。本文介紹采用多種EDA工具進行FPGA設計的實現原理及方法,并以實際操作介紹了整個FPGA的設計流程。

1.數字邏輯劃分與FPGA結構

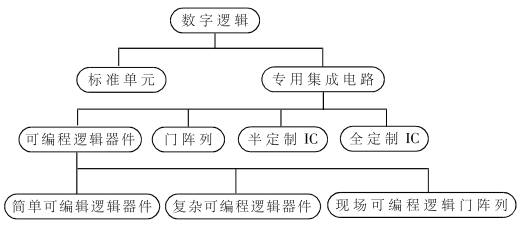

圖1所示為數字邏輯權狀分類圖,由其可以看出,現場可編程門陣列(FPGA)是專用集成電路中可編程邏輯器件的重要分支。隨著微電子工業的發展與進步,FPGA的集成度已經達到數百萬門,如Xilinx公司的Xcv3200e最大門數為320萬門,Altera公司的Apex20k1500e為150萬門,且系統時鐘頻率已達到200MHz,支持多種I/I電壓標準,并具有豐富的可重復利用的IP核,便于加速系統設計。

FPGA的內部資源(以Xilinx公司為例)一般分為可編程邏輯塊CLB、輸入輸出塊IOB和可編程連線PI三部分。通過編程控制PI連接各CLB單元,可以形成具有特定功能的電路。使用各公司的專用設計軟件設計FPGA,最終可形成由PI控制CLB單元的位流文件。

圖1 數字邏輯樹狀分類圖

Xilinx公司主推的Virtex系列FPGA產品采用0.22微米工藝,具有如下特性:支持9種I/O標準、4個延時鎖定環、塊存儲與分布存儲并存、可編程流水延時存儲、熱控制、配置速率為500Mb/s。而Altera公司的Apex20ke系列同樣是其公司主推的FPGA產品,在內部嘏線資源方面與Xilinx公司產品不同。在Virtex器件中,分為雙長線、單長線、長線幾種,在布線時可以按最近原則進行取舍;而在Apex20ke中,連線僅為一種等長,所以在時序分析時比較準確。

2.FPGA設計流程

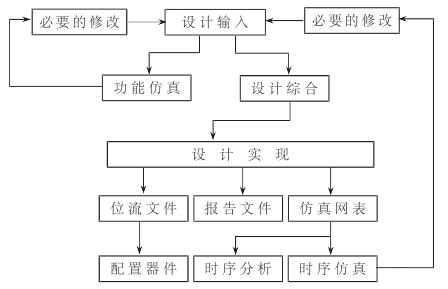

FPGA設計人體分為設計輸入、綜合、功能仿真(前仿真)、實現、時序仿真(后仿真)、配置下載等六個步驟,設計流程如圖2所示。下面分別介紹各個設計步驟。

圖2 FPGA設計流程圖

2.1設計輸入

設計輸入包括使用硬件描述語言HDL、狀態圖與原理圖輸入三種方式。HDL設計方式是現今設計大規模數字集成電路的良好形式,除IEEE標準中VHDL與Verilog HDL兩種形式外,尚有各自FPGA廠家推出的專用語言,如Quartus下的AHDL。HDL語言描述在狀態機、控制邏輯、總線功能方面較強,使其描述的電路能特定綜合器(如Synopsys公司的FPGA Compiler II或FPGA Express)作用下以具體硬件單元較好地實現;而原理圖輸入在頂層設計、數據通路邏輯、手工最優化電路等方面具有圖形化強、單元節儉、功能明確等特點,另外,在Altera公司Quartus軟件環境下,可以使用Momory Editor對內部memory進行直接編輯置入數據。常用方式是以HDL語言為主,原理圖為輔,進行混合設計以發揮二者各自特色。

通常,FPGA廠商軟件與第三方軟件設有接口,可以把第三方設計文件導入進行處理。如Quartus與FoundaTIon都可以把EDIF網表作為輸入網表而直接進行布局布線,布局布線后,可再將生成的相應文件交給第三方進行后續處理。

2.2設計綜合

綜合,就是針對給定的電路實現功能和實現此電路的約束條件,如速度、功耗、成本及電路類型等,通過計算機進行優化處理,獲得一個能滿足上述要求的電路設計方案。也就是是說,被綜合的文件是HDL文件(或相應文件等),綜合的依據是邏輯設計的描述和各種約束條件,綜合的結果則是一個硬件電路的實現方案,該方案必須同時滿足預期的功能和約束條件。對于綜合來說,滿足要求的方案可能有多個,綜合器將產生一個最優的或接近最優的結果。因此,綜合的過程也就是設計目標的優化過程,最后獲得的結構與綜合器的工作性能有關。

FPGA Compiler II是一個完善的FPGA邏輯分析、綜合和優化工具,它從HDL形式未優化的網表中產生優化的網表文件,包括分析、綜合和優化三個步驟。其中,分析是采用Synopsys標準的HDL語法規則對HDL源文件進行分析并糾正語法錯誤;綜合是以選定的FPGA結構和器件為目標,對HDL和FPGA網表文件進行邏輯綜合;而優化則是根據用戶的設計約束對速度和面積進行邏輯優化,產生一個優化的FPGA網表文件,以供FPGA布局和布線工具使用,即將電路優化于特定廠家器件庫,獨立于硅持性,但可以被約束條件所驅動。

利用FPGA Compiler II進行設計綜合時,應在當前Project下導入設計源文件,自動進行語法分析,在語法無誤并確定綜合方式、目標器件、綜合強度、多層保持選擇、優化目標等設置后,即可進行綜合與優化。在此可以將兩步獨立進行,在兩步之間進行約束指定,如時鐘的確定、通路與端口的延時、模塊的算子共享、寄存器的扇出等。如果設計模型較大,可以采用層次化方式進行綜合,先綜合下級模塊,后綜合上級模塊。在進行上級模塊綜合埋設置下級模塊為Don't Touch,使設計與綜合過程合理化。綜合后形成的網表可以以EDIF格式輸出,也可以以VHDL或Verilog HDL格式輸出,將其導入FPGA設計廠商提供的可支持第三方設計輸入的專用軟件中,就可進行后續的FPGA芯片的實現。綜合完成后可以輸出報告文件,列出綜合狀態與綜合結果,如資源使用情況、綜合后層次信息等。

2.3仿真驗證

從廣義上講,設計驗證包括功能與時序仿真和電路驗證。仿真是指使用設計軟件包對已實現的設計進行完整測試,模擬實際物理環境下的工作情況。前仿真是指僅對邏輯功能進行測試模擬,以了解其實現的功能否滿足原設計的要求,仿真過程沒有加入時序信息,不涉及具體器件的硬件特性,如延時特性;而在布局布線后,提取有關的器件延遲、連線延時等時序參數,并在此基礎上進行的仿真稱為后仿真,它是接近真實器件運行的仿真。

2.4 設計實現

實現可理解為利用實現工具把邏輯映射到目標器件結構的資源中,決定邏輯的最佳布局,選擇邏輯與輸入輸出功能連接的布線通道進行連線,并產生相應文件(如配置文件與相關報告)。通常可分為如下五個步驟。

(1)轉換:將多個設計文件進行轉換并合并到一個設計庫文件中。

(2)映射:將網表中邏輯門映射成物理元素,即把邏輯設計分割到構成可編程邏輯陣列內的可配置邏輯塊與輸入輸出塊及其它資源中的過程。

(3)布局與布線:布局是指從映射取出定義的邏輯和輸入輸出塊,并把它們分配到FPGA內部的物理位置,通常基于某種先進的算法,如最小分割、模擬退火和一般的受力方向張弛等來完成;布線是指利用自動布線軟件使用布線資源選擇路徑試著完成所有的邏輯連接。因最新的設計實現工具是時序驅動的,即在器件的布局布線期間對整個信號通道執行時序分析,因此可以使用約束條件操作布線軟件,完成設計規定的性能要求。在布局布線過程中,可同時提取時序信息形成報靠。

(4)時序提取:產生一反標文件,供給后續的時序仿真使用。

(5)配置:產生FPGA配置時的需要的位流文件。

在實現過程中可以進行選項設置。因其支持增量設計,可以使其重復多次布線,且每次布線利用上一次布線信息以使布線更優或達到設計目標。在實現過程中應設置默認配置的下載形式,以使后續位流下載正常。

2.5時序分析

在設計實現過程中,在映射后需要對一個設計的實際功能塊的延時和估計的布線延時進行時序分析;而在布局布線后,也要對實際布局布線的功能塊延時和實際布線延時進行靜態時序分析。從某種程序來講,靜態時序分析可以說是整個FPGA設計中最重要的步驟,它允許設計者詳盡地分析所有關鍵路徑并得出一個有次序的報告,而且報告中含有其它調試信息,比如每個網絡節點的扇出或容性負載等。靜態時序分析器可以用來檢查設計的邏輯和時序,以便計算各通中性能,識別可靠的蹤跡,檢測建立和保持時間的配合,時序分析器不要求用戶產生輸入激勵或測試矢量。

雖然Xilinx與Altera在FPGA開發套件上擁有時序分析工具,但在擁有第三方專門時序分析工具的情況下,僅利用FPGA廠家設計工具進行布局布線,而使用第三方的專門時序分析工具進行時序分析,一般FPGA廠商在其設計環境下皆有與第三方時序分析工具的接口。Synopsys公司的PrimeTIme是一個很好的時序分析工具,利用它可以達到更好的效果。將綜合后的網表文件保存為db格式,可在PrimeTIme環境下打開。利用此軟件查看關鍵路徑或設計者感興趣的通路的時序,并對其進行分析,再次對原來的設計進行時序結束,可以提高工作主頻或減少關鍵路徑的躚 時。與綜合過程相似,靜態時序分析也是一個重復的過程,它與布局布線步驟緊密相連,這個操作通常要進行多次直到時序約束得到很好的滿足。

在綜合與時序仿真過程中交互使用PrimeTIme進行時序分析,滿足設計要求后即可進行FPGA芯片投片前的最終物理驗證。

2.6下載驗證

下載是在功能仿真與時序仿真正確的前提下,將綜合后形成的位流下載到具體的FPGA芯片中,也叫芯片配置。FPGA設計有兩種配置形式:直接由計算機經過專用下載電纜進行配置;由外圍配置芯片進行上電時自動配置。因FPGA具有掉電信息丟失的性質,因此可在驗證初期使用電纜直接下載位流,如有必要再將燒錄配置芯片中(如Xilinx的XC18V系列,Altera的EPC2系列)。使用電纜下載時有多種直載方式,如對Xilinx公司的FPGA下載可以使用JTAG Programmer、Hardware Programmer、PROM Programmer三種方式,而對Altera公司的FPGA可以選擇JTAG方式或Passive Serial方式。因FPGA大多支持IEEE的JTAG標準,所以使用芯片上的JTAG口是常用下載方式。

將位流文件下載到FPGA器件內部后進行實際器件的物理測試即為電路驗證,當得到正確的驗證結果后就證明了設計的正確性。電路驗證對FPGA投片生產具有較大意義。

3.多種EDA工具的FPGA設計

仿真工具Modelsim與綜合工具FPGA Compiler II及布線工具Foundation Series或Quartus相配合實現FPGA設計流程圖如圖3所示。

在設計輸入階段,因Modelsim僅支持VHDL或Verilog HDL,所以在選用多種設計輸入工具時,可以使用文本編輯器完成HDL語言的輸入,也可以利用相應的工具以圖形方式完成輸入,但必須能夠導出對應的VHDL或Verilog HDL格式。近年來出現的圖形化HDL設計工具,可以接收邏輯結構圖、狀態轉換圖、數據流圖、控制流程圖及真值表等輸入方式,并通過配置的翻譯器將這些圖形格式轉化為HDL文件,如Mentor Graphics公司的Renoir,Xilinx公司的Foundation Series都帶有將狀態轉換圖翻譯成HDL文本的設計工具。在這方面,Summit公司(現在已經合并為Innoveda)的圖形化界面友好程度較高,且可以導出相應的HDL格式。

從圖3中可以看到有三處可以由Modelsim進行仿真:第一處是寄存器傳輸級(RTL)仿真,此級仿真是對設計的語法和基本功能進行驗證(不含時序信息);第二處是針對特定的FPGA廠有技術的仿真,此級偽真是在綜合后、實現前而進行的功能級仿真,功能級仿真一般驗證綜合后是否可以得到設計者所需要的正確功能;第三處仿真是門級仿真,此級仿真是針對門級時序進行的仿真,門級仿真體現出由于布局布線而產生的實際延時。

在RTL仿真階段,應該建立一個測試臺。此測試臺可以在整個FPGA流程中進行仿真驗證(RTL級、功能級、時序門級)。測試臺不但提供測試激勵與接收響應信息,而且可以測試HDL仿真流程中的關鍵功能(如運算部件輸出值的正確性等)。測試臺的產生可以直接使用文本編程得到,也可以使用圖形化工具輸入,再由軟件翻譯為HDL格式,例如使用HDL Bencher軟件利用其良好的波形輸入界面輸入測試激勵,再由其自動轉化為HDL格式而得到。

在功能級仿真階段,一般驗證綜合后是否仍與RTL級仿真結果相同。

圖3 實現FPGA設計流程圖

在門級仿真階段,由于已經針對具體的FPGA廠家技術進行了功能級仿真,因此可以通過布局布線得到標準延格式下的時序信息進行門級仿真。

Mentor Graphics公司的Modelsim是業界較好的仿真工具,其仿真功能強大,且圖形化界面友好,而且具有結構、信號、波形、進程、數據流等窗口。將FPGA設計(以HDL方式)輸入后進行編譯即可進行前仿真,其最新版本Modelsim SE/Plus 5.5支持VHDL與Verilog HDL混合仿真。在仿真時可以編寫HDL激勵文件或執行組模式方式。組模式方式類似批處理方式,可以連續執行事先在文件中寫好的多個執行命令,這對重新仿真或重復執行多個命令特別有效。在仿真過程中可以執行性能分析與代碼覆蓋分析。性能分析在程序代碼執行過程中可以分析出各部分代碼執行時占用整個執行時間的百分率。在此信息下,設計者可以找到設計的瓶頸并通過優化代碼減少仿真時間。代碼覆蓋分析可以使設計者確切知道在測試臺上正在進行的代碼位置,以方便設計者調試。

由Modelsim進行仿真,需要導出VHDL或Verilog HDL網表。此網表是由針對特定FPGA器件的基本單元組成的。這些基本單元在FPGA廠家提供的廠家庫中含有其定義和特性,且廠家一般提供其功能的VHDL或Verilog VDL庫。因此,在Modelsim下進行仿真,需要設置廠家庫信息。如使用Altera公司的Apex20ke系列,需要將Apex20ke_atoms.v(或.vhd)與Apex20ke_component.v文件設置或編譯到工程項目的對應庫中。除網表外,還需要布局布線輸出的標準延時文件(sdf),將sdf文件加入仿真可以在窗口化界面設置加入,或通過激勵指定。如使用Verilog HDL時加入反標語句$sdf_annotate(“”,Top)通過參數路徑指定即可。

在綜合階段,應利用設計指定的約束文件將RTL級設計功能實現并優化到具有相等功能且具有單元延時(但不含時序信息)的基本器件中,如觸發器、邏輯門等,得到的結果是功能獨立于FPGA的網表。它不含時序信息,可作為后續的布局布線使用。使用FPGA Compiler II進行綜合后可以導出EDIF網絡。

在實際階段,主要是利用綜合后生成的EDIF網表并基于FPGA內的基本器件進行布局布線。可以利用布線工具Foundation Series選用具體器件(如Virtex系列器件)進行布局布線加以實現,也可以使用布線工具Quartus選用Apex20ke系列器件進行布局布線加以實現,同時輸出相應的VHDL或Verilog HDL格式,以便在Modelsim下進行仿真。

結束語

以上就是采用多種EDA工具的FPGA設計介紹了。在數字系統設計的今天,采用多種EDA工具進行處理,同時使用FPGA快速設計專用系統或作為檢驗手段,已經成為數字系統設計中不可或缺的一種方式,了解并熟悉其設計流血應成為現今電子工程師的一種必備知識。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹