在進行小數分頻頻率合成器的芯片測試時,數字部分可以通過常規的數字測試方法即可以實現;而輸出射頻信號的相位噪聲、雜散噪聲則需要芯片工作在正常的輸出狀態下才能測試;因此小數分頻頻率合成器芯片在測試時需要與外接環路濾波器(LF)、壓控振蕩器(VCO)才能構成完整的鎖相環回路,在具備正常的芯片功能的前提下才能實現對其相位噪聲、雜散噪聲下的測試。本文以ADF4153小數分頻頻率合成器為例,研究了其外圍環路濾波器的設計方法,給出了基于芯片測試的環路濾波器設計流程,并進行了驗證測試。

1.外接環路濾波器設計

環路濾波器是電荷泵鎖相環電路的重要環節,它連接在電荷泵和壓控振蕩器之間。鎖相環的基本頻率特性是由環路濾波器決定的。實際上,正是由于環路濾波器的存在,鎖相環才可以選擇工作在任意的中心頻率和帶寬內。環路濾波器的類型多種多樣,大致分為有源濾波器和無源濾波器兩大類,無源濾波器與有源濾波器相比,其優點在于:結構簡單、低噪聲、高穩定度和易以實現。

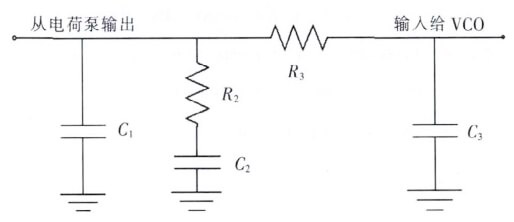

最常見的無源濾波器是如圖1所示的三階濾波器。一般而言,環路濾波器的帶寬應為PFD頻率(通道間隔)的1/10.提高環路帶寬會縮短鎖定時間。但環路帶寬過大會大幅度地增加不穩定性,從而導致鎖相環無法鎖定的狀態。

圖1 三階環路濾波器

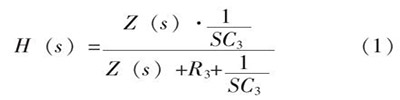

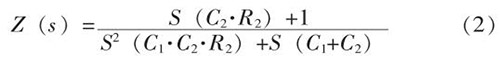

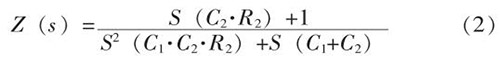

三階無源濾波器的傳遞函數為:

其中:

聯合公式(1)、(2)可以得出:

其中:K0=C2R2,K1=C1C2C3R2R3,K2=[(C1+C2)C3R3+(C1+C3)C2R2],K3=C1C2C3。

為了求取C1、C12、C3和R1、R2的取值,首先需要確定設計需要的帶寬及相位裕度,諸多文獻給出了詳細的求取步驟,在此不再敷述。然而,在實際的應用時,這種計算方法較為繁瑣,不利于工程設計使用。

ADI公司發布的ADIsimPLL頻率合成器設計軟件可以很方便地根據用戶的使用要求進行環路濾波器的設計。它將應用工程師從繁雜的數學計算中解脫出來。應用者只要輸入設置環路濾波器的幾個關鍵參數,ADISimPLL就可以自動地計算出所需要的濾波器元器件的數值。這些參數包括:鑒相頻率PFD,電荷泵電流ICP,環路帶寬BW,相位裕度,VCO控制靈敏度Kv,濾波器的形式(有源或無源,階數)。然而,在芯片測試時,如何盡可能地將外界電路(如環路濾波器)引入的噪聲降低,以測試出芯片的真實性能,這是芯片外圍電路設計時需要解決的問題。

2.設計參數選擇

為了研究環路濾波器對鎖相環輸出頻率相位噪聲的影響,設計出符合芯片測試需要的外圍環路濾波器。本文在ADIsimPLL軟件中進行了如下仿真配置。器件型號:ADF 4153,fPFD=25MHz(理想信號源),INT=69,FRAC=101,MOD=125,VCO采用ZComm公司的V674ME34-LF,在該配置下,預期輸出的RFOUT=1.7452GHz。

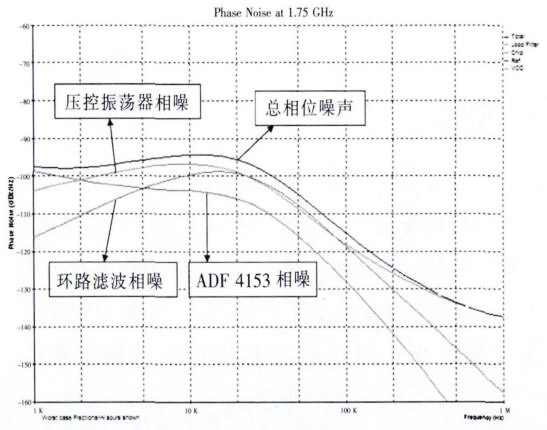

(a)設定環路濾波器帶寬為20kHz,相位裕度50°,其相位噪聲的仿真情況如圖2所示。

圖2 環路帶寬20kHz時的相位噪聲仿真圖

從圖2中可以得知,當環路濾波帶寬為20kHz時,VCO所引起的相位噪聲占據了主導地位。芯片所引起的相位噪聲則被淹沒在總輸出噪聲之下。換句話說,當環路帶寬較窄(如20kH)的情況下,針對鎖相環輸出信號進行相位噪聲測試,其結果并不能真正地反映芯片輸出的相位噪聲。

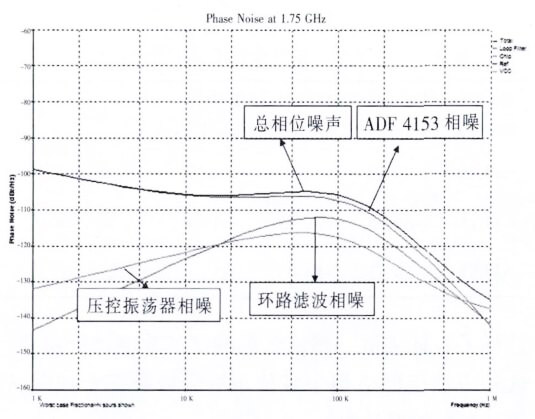

(b)設定環路濾波器帶寬為100kHz,相位裕度50°,其相位噪聲的仿真情況如圖3所示。

圖3 環路帶寬為100kHz時的相位噪聲仿真圖

從圖3中可以得知,當環路濾波帶寬為100kHz時,VCO對于總相位噪聲的貢獻顯著地降低,芯片所引起的相位噪聲占據了主導地位,在10kHz以內,總相位噪聲輸出的曲線基本與芯片所引起的相位噪聲重合。由此可以得知,當環路帶寬較寬(如100kHz)的情況下,針對鎖相環輸出信號進行相位噪聲測試,其結果基本能真正反映芯片輸出的相位噪聲。

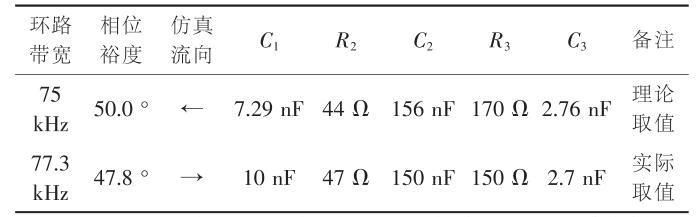

本文研究的ADF 4154的主要測試頻點為1.7452GHz(fPFD=25MHz,RSET=5.1k),根據測試要求進行綜合的考慮,設定了環路帶寬75kHz,相位裕度50°的約束條件。在進行ADF 4153的外圍電路設計時,首先需要確認所使用的VCO型號及其標稱性能。然后再根據ADI公司提供的ADIsim-PLL軟件進行三階環路濾波器的設計。從軟件得出C1~C3、R2、R3的具體取值,再根據現有的標稱電容電阻值進行調整,反算出實際設計的環路帶寬及相位裕度。實際數據如表1所示。

表1三階環路濾波器電容與電阻的取值

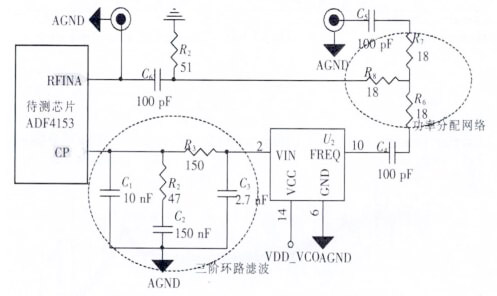

由此,我們確定了環路濾波器中各個電容、電阻的取值,并設計了可用于ADF 4153芯片測試的電路原理圖,如圖4所示。VCO的輸出不僅需要連接外部頻譜儀進行測試,還需要通過電容反饋到ADF 4153的REFINA端,同時REFINA端還需要預留SMA頭用于射頻輸入頻率范圍及靈敏度測試。一個簡單的電阻網絡用于完成VCO輸出信號功率的再分配。

圖4 環路濾波器及射頻電路設計

3.測試驗證

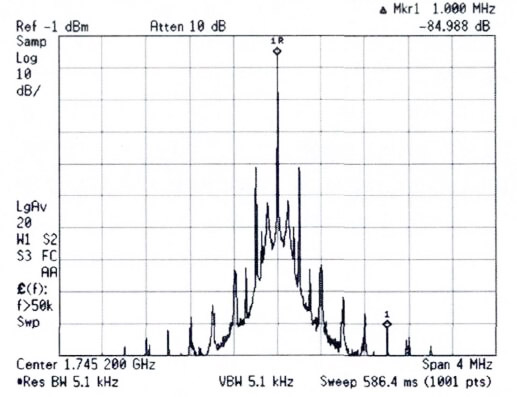

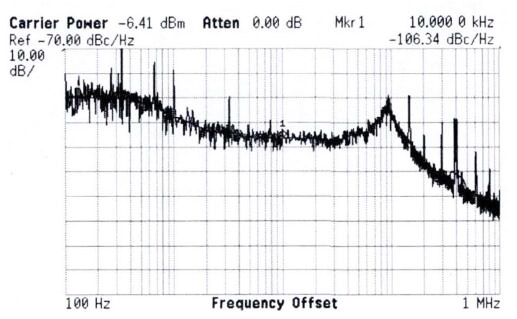

在仿真的基礎上,本文設計并加工了ADF4153的測試板,并按照計算的電容、電阻值組成了環路濾波網絡。采用Agilent8257D射頻信號源提供250MHz作為fREFIN,通過SPI端口設定fPFD=25MHz,N=69,4/5分頻模式,ICP=5mA,FRAC=101,MOD=125。使用頻譜儀測量輸出信號,能夠正常鎖定在1.7452GHz,如圖5所示。圖6為該頻點的相位噪聲測試圖,實測相位噪聲為-106.34dBc/Hz.環路帶寬約為85kHz,與理論值77.3kHz存在一定的差距。這是由于在仿真時并沒有考慮測試板走線及測試插座等存在的寄生電容所導致的偏差,但仍在合理范圍以內。

圖5 輸出信號頻譜

圖6 相位噪聲測試圖

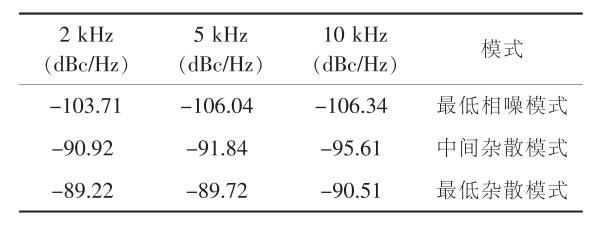

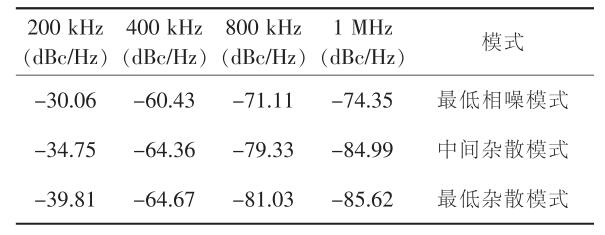

針對芯片進行不同工作模式下的相位噪聲及雜散進行測試,測試結果如表2、3所示。

表2不同模式的相位噪聲測試數據

表3不同模式下的雜散測試數據

數據手冊規定最低的相位噪聲模式下5kHz頻偏的相位噪聲PN≤-95dBc/Hz,實測該點為-106.04dBc/Hz,測試結果滿足要求。

數據手冊規定中間雜散模式下1MHz頻偏的雜散SN≤-65dBc/Hz,實測該點為-84.99dBc/Hz,測試結果滿足要求。

綜上所述,該濾波器的設計能達到預期的設計目標,滿足不同模式下的雜散及相噪測試的要求,可用于ADF 4153芯片的性能測試。

小結

以上就是基于芯片測試的環路濾波器設計介紹了。本文主要基于芯片測試目的,針對外圍電路中的環路濾波器設計來進行討論,從而給出一種簡單、易行的工程化計算方法和流程,并對其進行了驗證測試,測試結果滿足芯片測試的需要。目前這種方法已經應用于多款小數分頻頻率合成器的測試電路的設計中。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹