作為通道技術和網絡技術結合的產物,光纖通道(fibre channel)是一種具有高實時性、高可靠性、高帶寬,高性價比的開放式網絡。任何需要接入到光纖通道網絡的設備都需要相應的網絡接口卡(NAC),而網絡接口卡的核心是接口控制芯片。由于光纖通道標準是一項十分龐大而復雜的協議,不同的特性適用于不同的應用環境;又因為光纖通道標準目前仍處于發展階段,標準的內容還在做不停的變化,因此選用FPGA作為當前接口控制芯片的載體是一個非常合適的選擇。一方面對于不同的應用環境,可以對相應的功能模塊進行適當的裁減,既能滿足應用需要又能降低成本;另一方面對于協議的變化,基于FPGA的實現也很容易就能對老版本設計進行更新。

1.協議分析

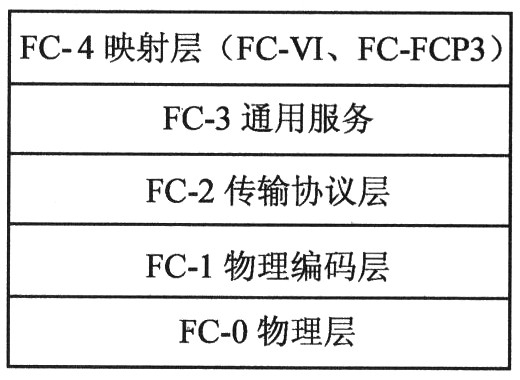

和OSI參考模型類似,光纖通道協議簇也是以分層的方式來組織各個協議的。其分層模型如圖1所示。

圖1 光纖通道分層模型

作為數據傳輸協議,光纖通道支持許多上層協議,包括VIA、SCSI、IPv4、IPv6、SBCCS、ASM等。在為這些協議傳輸數據之前,需要先將待發送的數據映射成規定的格式,FC-4層實現這一映射,對于每一個支持的上層協議,都有一個映射協議與之相對應。

FC-3層是一個通用服務層,為映射層協議提供一系列通用服務。比較重要的幾個服務包括:交換注冊、端口注冊和注銷服務。

FC-2層是光纖通道協議中最重要的一層,定義了將數據塊進行端到端傳輸的規則和機制,包括不同類型的服務、幀格式定義、序列的分片和重裝、交換管理、地址分配和多播管理等。

FC-1層定義了串行編碼和解碼規范,規定使用8B/10B編碼。

FC-0層是光纖通道協議的物理層規范,定義了發射機、接收機、傳輸介質以及它們之間的接口規范。傳輸速率也在這里定義。

2.設計方案

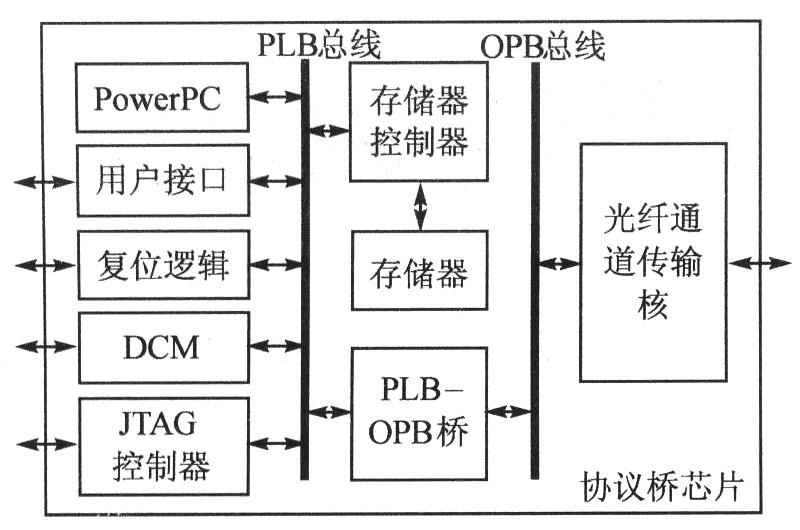

通過對協議的分析得出,映射層協議和具體應用環境密切相關,應該由用戶自己實現。接口控制芯片在邏輯上可以分成三部分,即通用服務模塊、端到端IU傳輸和緩沖到緩沖幀傳輸;在實現方式上又可以分為軟件部分和硬件部分。接口控制芯片系統框圖如圖2所示。

圖2 接口控制芯片系統組成

圖2左邊的PowerPC和存儲器控制器通過PLB總線互聯在一起,構建了Linux操作系統和接口控制芯片的軟件部分的運行平臺。

PowerPC架構中還包含了通用的OPB總線,用來進行外部設備的互聯。OPB總線通過一個PLB-OPB橋連接到PLB總線,如圖2右邊所示。連接到OPB總線的外部設備只有一個,也就是光纖通道傳輸核。

用戶接口定義了接口控制芯片的用戶接口。根據應用環境的不同,這個模塊有不同的實現方法,如PCI或USB。

當用戶有數據需要發送時,通過接口控制芯片的用戶接口將數據按標準格式存人芯片內部的數據存儲器,并通過設置相應的寄存器請求接口控制芯片的數據傳輸服務。然后,軟件代碼將數據接管過來,先為這次數據(IU)傳輸分配相應的軟件資源(交換狀態塊、序列狀態塊等)用以記錄數據的發送狀態。等完成相應的處理后,PowerPC通過光纖通道傳輸核提供的接口通知傳輸核對數據進行處理,包括分片、成幀、CRC計算和8B/10B編碼等任務。最后,傳輸核通過輸出引腳輸出高速串行數據去調制光發射機并發送到光纖鏈路。

當從輸入鏈路上接收到數據時,傳輸核首先對數據進行處理,包括位同步、串并轉換、8B/10B解碼、字同步、有序集檢測、CRC校驗和幀提取。當有效幀接收到并存到接收緩沖區后,硬件模塊設置相應的寄存器通知Power-PC,然后PowerPC對接收到的幀進行處理,包括分配相應的軟件資源、幀重裝。當屬于一個序列的所有幀都正確接收完后,PowerPC通過用戶接口模塊通知用戶模塊,用戶模塊接收到數據后自行進行處理。

3.硬件設計

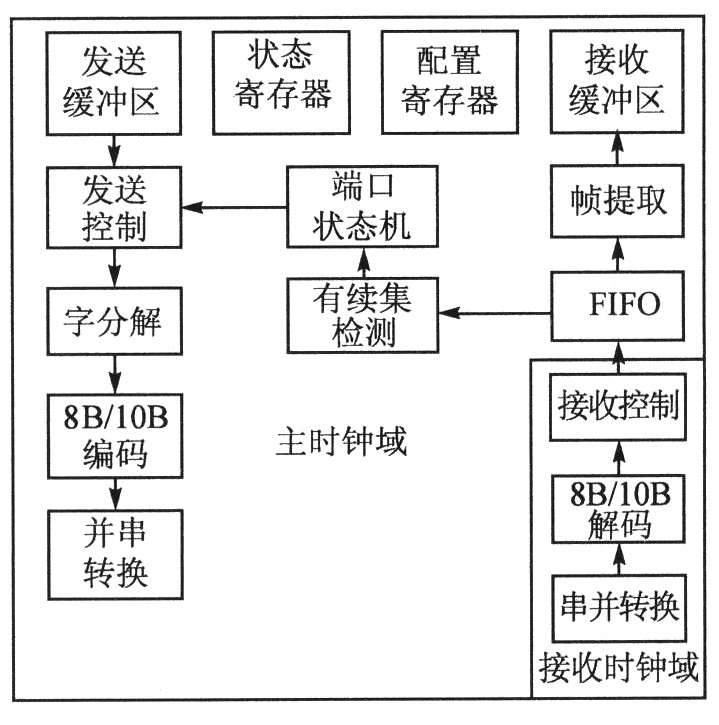

接口控制芯片的硬件部分也就是圖2中的光纖通道傳輸核,負責將數據幀按標準規定的格式從發送緩沖區傳輸到鏈路另一端的接收緩沖區。為了正確有效地完成這個任務,接口控制芯片的硬件部分實現以下一些功能:緩沖到緩沖的流量控制、鏈路級別的差錯檢測和恢復、字同步、有序集檢測、幀提取、8B/10B編解碼和串并/并串轉換等功能。接口控制芯片的硬件部分功能框圖如圖3所示。

圖3 光纖通道傳輸核

3.1發送控制邏輯

發送控制邏輯的功能是控制幀、原語信號和原語序列的發送順序,使之符合光纖通道標準,主要包括保證連續幀之間具有足夠的間隔和在幀之間插入原語信號。

發送幀的CRC值也由發送控制邏輯計算,傳統的串行計算方法達不到要求的速率,這里采用并行CRC算法進行計算,每個時鐘有效沿可以計算32位數據,大大提高了數據吞吐量。

緩沖到緩沖流量控制也在發送控制邏輯中實現。發送控制邏輯維持一個計數器,表示當前已發送但還未被確認的幀的數目,每當發送1幀,計數器加1;當接收到 R_RDY原語信號時,計數器減1。如果這個值小于配置寄存器中的BB_Credit值,則表示可以繼續發送幀;否則,表明目標端口已經沒有可用的接收緩沖區,發送控制邏輯此時就不往外發出幀。

3.2接收控制邏輯

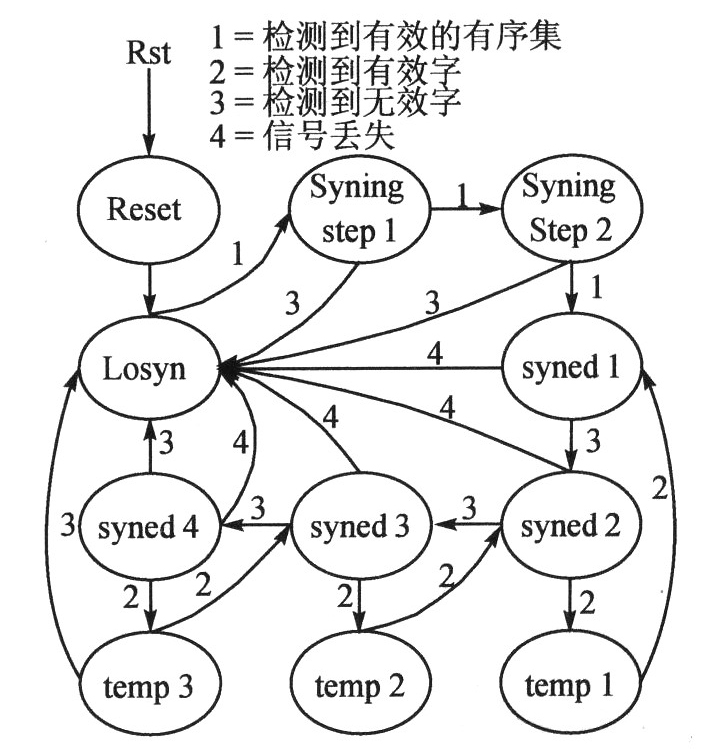

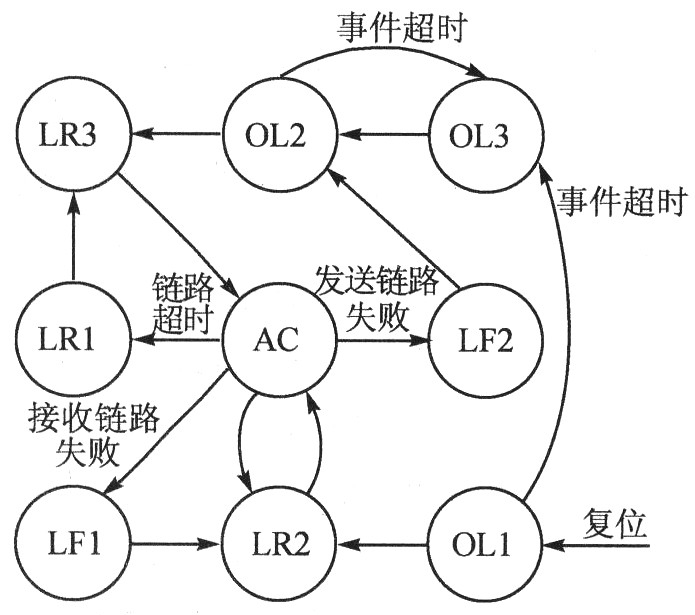

8B/10B解碼出來的數據是字節數據,而所有的有序集都是字,因此需要在輸入的字節流中正確區分出字邊界。接收控制邏輯內部的字同步模塊和接收狀態機協同工作,實現這一功能。標準規定的接收機狀態轉換圖如圖4所示。

圖4 接收機狀態轉換圖

3.38B/10B編解碼

傳統的編解碼方法由數字邏輯實現,主要是為了節省邏輯資源。由于FPGA內含有豐富的RAM,使其作為編解碼的載體既可以降低復雜程度又可以提高編解碼的速度,待編碼的數據作為地址線輸人,編碼數據存在RAM內從數據線輸出。

3.4端口狀態機

作為鏈路級差錯檢測與恢復的核心,端口狀態機對收發鏈路的狀態進行監測。每當鏈路狀態出現異常,端口狀態機就根據異常的起因啟動不同的鏈路恢復協議來對鏈路進行恢復。如果恢復失敗,那么端口狀態機就通過狀態寄存器向上層報告。出于版面的考慮,簡化的端口狀態機的狀態轉換圖如圖5所示。

圖5 端口狀態機狀態轉換圖

3.5其他模塊

異步FIFO:由于接口控制芯片的接收部分使用從接收數據中恢復出來的時鐘,因此和芯片的主時鐘是異步的。當將接收到的數據交給其他工作于主時鐘的模塊處理時需要進行速率調整。異步FIFO用于實現這個功能。串并/并串轉換:高速的串并轉換對器件性能有較高要求。FPGA內部集成了專用的硬核 (RocketIO)用來實現這一功能,因此對其進行適當的配置即可。這樣節省了專用的串并轉換芯片。

配置寄存器存儲一系列的工作參數,如(R_T_TOV、E_D_TOV等),復位后以默認值初始化寄存器。完成注冊后,使用新值更新寄存器。

光纖通道傳輸核通過狀態寄存器來表示自己當前所處的狀態(如在線、離線等)。

4.軟件設計

接口控制芯片的軟件部分負責進行參數協商和處理與端到端數據傳輸相關的事務,包括端口注冊和交換注冊、提供不同類型的服務、端到端流量控制、序列級差錯檢測和恢復。

為了簡化軟件的設計,以嵌人式Linux操作系統作為接口控制芯片的軟件運行環境。通過設計一系列的操作函數,實現整個軟件系統。最重要的函數包括:端口注冊函數、IU發送函數和接收幀處理函數。

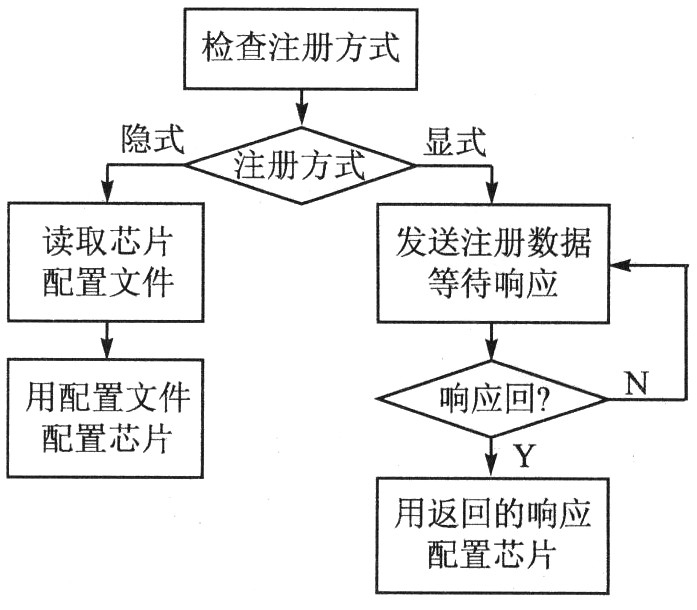

4.1端口注冊函數PLogin_in()

注冊包含端口注冊和交換注冊。兩種注冊的流程類似,這里僅分析端口注冊。系統啟動后,需要對芯片的工作參數進行配置,注冊函數根據用戶的配置選擇注冊方式。如果用戶指定隱式注冊,那么注冊函數從配置文件中讀取默認配置參數配置芯片;如果用戶指定顯式注冊,那么注冊函數發送注冊請求,等對方端口返回響應后,注冊函數用響應的數據配置參數。端口注冊函數的工作流程如圖6所示。

圖6 IU注冊流程

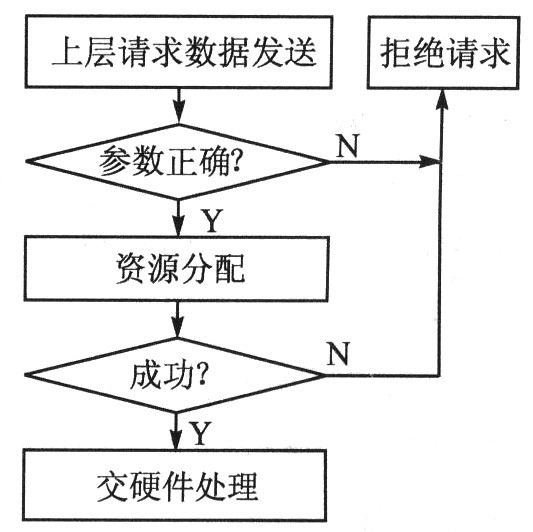

4.2IU發送函數Sen

圖7 IU發送流程

4.3接收幀處理函數Frm_Rcved()

當光纖通道傳輸核將正確的幀接收到并存儲于接收緩沖區后,通過狀態接口通知PowerPC。此時Frm_Rcved()函數開始處理幀頭,幀頭中需要檢查的參數很多,這里不在贅述。如果幀頭中的參數沒有錯誤,那么函數為這個新接收到的幀分配存儲空間,然后從接收緩沖區中將幀取到存儲器中,并以一定的方式和之前接收到的幀關聯起來(例如鏈表);如果幀頭中的參數有誤,則將幀丟棄并啟動中止序列協議進行序列恢復。

結語

本文總結了基于FPGA的光纖通道接口控制芯片設計方案,采用Verilog實現了接口控制芯片的RTL設計并完成了功能仿真和驗證,并通過嵌入式PowerPC完成了接口控制芯片的控制軟件設計;以Virtex-II Pro系列FPGA為平臺,實現了接口控制芯片原型。該設計具有極大的靈活性和可擴展性,在不同的應用環境中只需要對相應的軟硬件代碼進行適當的裁減或擴展即可,無需對PCB電路進行任何更改,具有極其廣泛的應用價值。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹