晶振是各整機電子設備的核心部件,它在一定程度上決定著整機的性能指標。晶振的相位噪聲指標是影響信號源的關鍵因素之一,對整機設備的性能參數有著重要意義,也是晶振非常關鍵的指標。本文介紹了一種小型超低相噪恒溫晶振的設計,重點闡述了有載品質因數(Q)值、電路結構等對相噪的影響,并基于改進型的巴特勒振蕩電路在小體積下進行了超低相噪恒溫晶振的設計,對其主振電路、放大電路、穩壓電路等進行了概要的分析。

1.理論分析

在晶體振蕩電路中,三極管、二極管和電阻、電容、電感等元件都存在噪聲,其中以產生振蕩信號的三極管噪聲影響最大;而電感、電容等元件,在噪聲分析中,可近似為無噪聲元件口。在放大器上加正反饋元件構成振蕩器時,噪聲將對振蕩器信號進行調制而形成白噪聲調相、白噪聲調頻和閃變噪聲調相、閃變噪聲調頻等噪聲模式。

根據LESSON模型分析,晶體振蕩器的相位噪聲與晶體振蕩電路的有載品質因數(Q)值密切相關,有載Q值越高,相位噪聲惡化的程度越低。因此在低相噪晶振設計中,通常圍繞如何提高有載Q值開展研究。晶體振蕩電路的有載Q值主要由振蕩電路中晶體諧振器自身Q值以及所采用的振蕩電路拓撲結構所決定。晶體諧振器自身的Q值受限于晶體制作工藝,不可能無限制提升,因此如何進一步提升晶體諧振器在振蕩電路中的有載Q值是低相噪晶振設計的關鍵。

常用的晶體振蕩電路主要有并聯反饋型振蕩電路和串聯反饋型振蕩電路。并聯振蕩電路中,晶體諧振器工作在串、并聯諧振頻率之問,晶體呈感性;常用的并聯振蕩電路包括皮爾斯電路和考畢茲電路。串聯振蕩電路是將晶體串聯在正反饋電路中,晶體諧振器工作在串聯諧振頻率,晶體呈純阻性。常用的串聯振蕩電路通常為巴特勒電路。

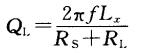

要提高晶體諧振器在電路的有載Q值,必須選取有載Q值匹配相對較好的振蕩電路形式。晶體的有載Q值為:

式中:L為晶體等效電感;R為晶體等效電阻;R為晶體負載電阻。

由于電路中的電阻損耗,電路中晶體諧振器有載Q值通常比晶體諧振器自身絕對Q值小。為使Q值損耗最小,應盡量使晶體的R最小,以便整個電路的Q值不會因負載電阻而顯著惡化。在皮爾斯電路和考畢茲電路等并聯振蕩電路中,晶體分別接在三極管的集電極和基極,等效負載相對較大;而在巴特勒串聯振蕩電路中,晶體諧振器串接在發射極來提供高頻負反饋,等效負載電阻小,有載Q值相對于前兩種電路有一定優勢。同時,采用并聯振蕩電路還需要加入晶體諧振器的B模抑制網絡,會進一步降低晶體諧振器Q值。因此,理論上高頻振蕩器采用串聯振蕩電路能達到比并聯振蕩電路更低的噪聲,在電路中具有良好的有載Q值。

2.仿真分析

電路拓撲結構確定后,在參數設計上,需進行充分的仿真驗證。對晶體振蕩器設計的仿真,重點要解決晶體諧振器和晶體管的建模問題,其次就是對振蕩電路結構的選擇,從而對晶體振蕩器的設計進行仿真分析,并對電路參數進行優化。

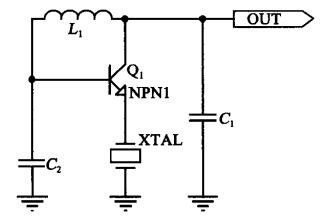

依據理論分析,為保證低相位噪聲水平,振蕩電路選擇了有載Q值良好的巴特勒串聯振蕩電路。在巴特勒電路中晶體串接在主振放大器的發射極,它提供高頻負反饋,而接在電路輸出端的電容分壓器提供正反饋。晶體諧振器在振蕩電路中工作在自身的串聯諧振頻率上,起到對諧振頻率進行高(選頻的作用)。巴特勒振蕩電路的交流等效圖如圖1所示。

圖1 等效電路圖

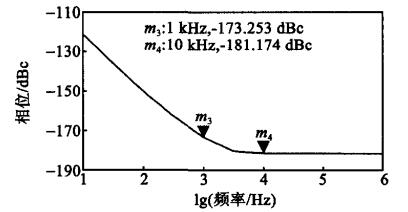

采用仿真手段,對上述振蕩電路進行仿真分析。圖2為采用諧波平衡仿真分析得到的相噪仿真結果。

圖2 相位噪聲仿真結果

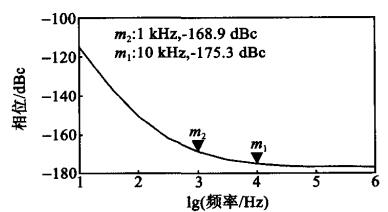

結合工程設計經驗,我們對巴特勒電路結構進行改進,將振蕩信號直接從石英諧振器引出,這樣可以充分利用晶體諧振器的高Q值選頻特性。改進后的巴特勒振蕩電路交流等效圖如圖3所示。

圖3 改進型等效電路圖

采用仿真工具,對改進型的巴特勒電路進行了分析,通過參數優化,得到的相噪仿真結果如圖4所示。

圖4 改進型相噪仿真結果

由圖4可看出,采用該改進型巴特勒結構的振蕩電路,相位噪聲有明顯改進。在產品實際設計中,會受到部分不確定附加噪聲的影響,相噪結果會與仿真分析存在偏差,但仿真分析仍然為產品的實際研制起到了一定的指導作用。

3.產品研制

3.1器件選型

在低相噪晶振設計中,器件選型是關系設計成敗的關鍵因素之一,特別是對晶體諧振器、三極管等關鍵器件的選擇。

在晶體諧振器的選擇上,對于切型、Q值、泛音次數、頻差、零溫度系數點(即拐點)、靜態電容、等效電阻等參數都要進行慎重考慮和正確選取,特別是在本文低相噪設計中,為保證電路中的高有載Q值,對晶體諧振器Q值的選擇尤其重要Es3。通過綜合考慮,本文選用了具有更高Q值和穩定性的SC切5次泛音高Q晶體諧振器。

在三極管的選擇上,本文重點考慮了噪聲系數,并兼顧高增益、低溫漂、小封裝等要求,噪聲系數<1最為理想。

在其他器件的選擇上,在滿足封裝要求的前提下,均重點考慮低噪聲的要求。

3.2電路設計

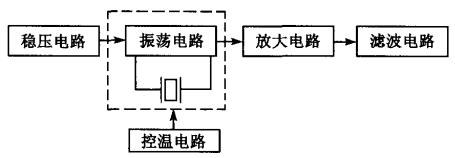

本設計中電路組成框圖如圖5所示。

圖5 晶振電路組成框圖

(1)振蕩電路

傳統的巴特勒結構電路將晶體諧振器連接在反饋回路中,振蕩模式較復雜,調試困難。本文對傳統巴特勒電路進行改進(見圖3),將振蕩信號直接從晶體諧振器引出,通過合理的電路及參數設計,可使輸出信號具有極低的相位噪聲。

(2)穩壓電路

晶體振蕩器對電源線上的噪聲尤其敏感,特別當晶振調諧范圍較寬時,因此低噪聲晶振振蕩電路的穩壓電路設計極其重要。在本設計中,我們選用低噪聲與紋波的線性穩壓器件,并連接到一個具有大的電源紋波抑制作用而同時具有低噪聲特性的運算放大器來作為供電單元。在電路板布局時,對電源濾波做充分考慮,使電源紋波對各級電路的影響達到最小。同時在變容二極管調諧端加入低噪聲運算放大器進行隔離,以有效降低調諧端噪聲電壓對晶振相位噪聲帶來的影響。

(3)放大電路

本設計中振蕩信號直接從晶體諧振器引出,因此選用具有更低輸入阻抗的共基極低噪聲放大器作為晶振的放大級,以便能與晶體諧振器更好地實現阻抗匹配,提高有載Q值。三極管選用低噪聲晶體管,其偏置電路使用與主振電路相同的低噪聲偏置,但放大器的直流工作點與主振電路不同,充分保證放大電路工作在線性狀態。同時在放大電路中加入適當的負反饋,降低閃爍調相(1/f)和閃爍調頻(1/f³)噪聲。

(4)濾波電路

本設計在輸出端加入了帶通濾波電路,使振蕩電路與輸出端有效隔離,減小負載變化對主振狀態的影響,同時提高輸出信號的頻譜純度。

(5)控溫電路

為保證晶振的短期穩定度及近端相噪,需采用精密控溫的方式來降低外界環境變化對晶振振蕩頻率的影響。本設計選擇了比例積分反饋的連續式控溫電路,通過PID比例積分反饋回路對溫度進行精確控制,提高控溫電路的靈敏度、控溫精度及環境適應性。

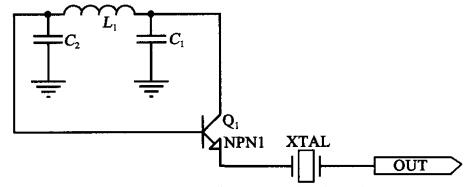

3.3測試結果

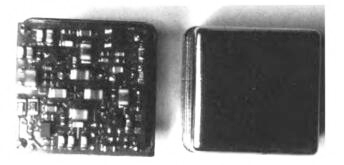

本文設計的100MHz小型超低相噪恒溫晶體振蕩器實物照片如圖6所示。

圖6 晶振實物照片

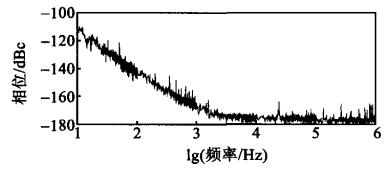

相位噪聲實際測試曲線如圖7所示。由圖可見,本文研制的100MHz小型超低相噪恒溫晶振體積達到20mm×20mm×10mm,相噪指標最優達到一168dBc/Hz@1kHz,達到了預期的研制目標。

圖7 相位噪聲測試曲線

結束語

本文總結了小型超低相噪恒溫晶振的設計方案。該文研制的100MHz小型超低相噪恒溫晶振體積達到20mm×20ram)<10mm,相噪指標最優達到一168dBc/Hz@1kHz,達到了預期的研制目標。其具備良好的相位噪聲性能及小封裝尺寸,可滿足新一代電子裝備對晶振體積和相噪指標的嚴苛要求,具備很好的應用前景。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹