為了實現高性價比、低相噪和低雜散的數字化信號源,本文提出了以直接數字頻率合成芯片AD9854 為核心的設計方案。并詳細論證了DSP、CPLD(comp lex p rogramm ab le logic device)、外部IO器件與AD9854相結合構成多功能信號源的硬件組成、功能擴展及其實現方法,還對輸出信號的品質進行了詳細分析,最后給出信號源樣機的主要技術指標。

1.信號源介紹

信號源是雷達、通信及其他電子系統不可缺少的重要組成部分。低相位噪聲、高穩定度、高可靠性和多功能信號源的研究受到普遍重視。目前實現信號源的主要技術有: 直接頻率合成、鎖相式頻率合成和直接數字頻率合成DDS。DDS具有極高的頻率分辨率、極快的頻率切換速度、頻率切換時相位連續、易于功能擴展和全數字化易于集成等優點。特別適合應用于信道間隔小、信道頻率數多和相位噪聲低的場合。文獻[3~6]詳細分析了DDS相位噪聲對其本身輸出波形品質的影響,指出相位噪聲主要由累加相位截斷、正弦表存儲器有限字長、DAC有限分辨率和內部噪聲等因素決定,DDS本身對相位噪聲的影響可以忽略。

2.總體設計

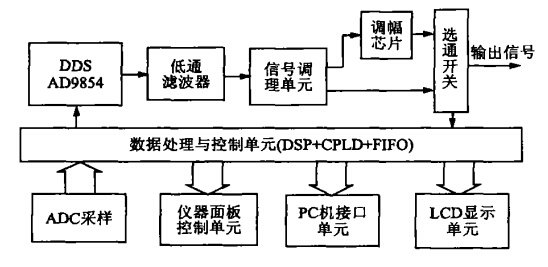

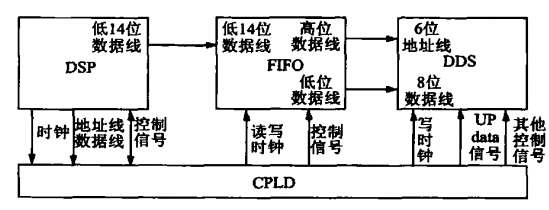

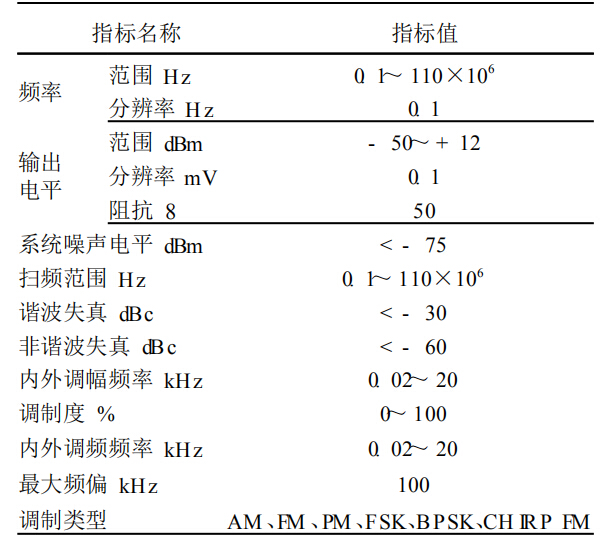

多功能信號源的硬件框圖,如圖1所示。系統由5個部分組成:數據處理與控制單元、DDS單元、模擬調制與數字調制單元、外調制信號采樣單元和輸入輸出接口單元。信號源要達到的主要技術指標,如表1所示。

圖1 信號源的總體結構框圖

表1 信號源的主要技術指標

DDS單元是系統的核心,本系統使用的AD9854是最高工作時鐘頻率為300MHz,功能非常強大的直接數字頻率合成器。一般情況下,DDS時鐘頻率的40%為實際輸出波形的最高頻率,AD9854時鐘頻率300MHz,則輸出波形的最高頻率可達120MHz。且根據參考文獻[7]中對其各類參數的描述,符合信號源的性能要求,所以選擇AD9854用于該信號源中。

2.1AD9854特點和功能

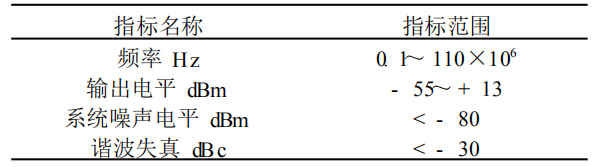

AD9854工作頻率高,IO端口功能豐富,其內部功能框圖如圖2所示。主要特點如下:

圖2 AD9854內部功能框圖

(1)工作頻率高達300MHz,片內有PLL(phase2locked loop ),可實現對參考頻率4~20倍頻,支持單端或差分時鐘源。推薦使用差分時鐘芯片產生差分時鐘信號,再通過片內PLL倍頻成300MHz。簡化了時鐘源的設計, 同時使低成本和低相位噪聲的參考時鐘源在技術上可行。

(2)雙頻率控制字,字長48位;雙相位控制字,字長14位。當工作頻率為300MHz時,頻率分辨率為1×10- 6Hz, 頻率轉換時間最小值為6.7 ns。

(3)具有良好的動態性能。在100MHz時輸出仍有80dB SDFR(無雜散動態范圍)。

(4)具有簡化的高速IO控制端口。10MHz的串行兩線或三線接口,8位并行100MHz端口。本系統因為要實現多種調制功能,需要快速刷新DDS內部的頻率、幅度和相位控制字,所以使用并行接口。

(5)2個300MHz高速12位DAC(digital2analoy converter),可以輸出正交信號,可以方便應用于調制和解調系統中。2個DAC都是差分電流型輸出, 都可以實現頻率、幅度和相位的獨立控制, 完成掃頻、調制和O SK 等功能。

(6)內置高速比較器,配合片上2個DAC,可以單片產生擴展脈沖信號,且占空比可調。

(7)片內可選5種工作模式:單頻、FSK、RAMPFSK、CHIPFM、BPSK。調制功能極其豐富,還可以配合片外芯片實現復雜的數字調制和模擬調制。

2.2系統硬件結構分析

在圖1中,鍵盤和LCD(liqw d crystal disp lay)構成人機交互的界面。用戶由鍵盤輸入參數,通過LCD顯示。同時單片機將數據通過HPI口送DSP,在DSP中進行處理,然后將處理后的數據在CPLD的協調下由8位并行口送入AD9854中。AD9854輸出頻率0.1H z~110MHz的正弦波,此信號是差分電流形式,需由電阻網絡轉變為電壓信號,再經過低通濾波器輸出。為了使信號輸出電平范圍滿足要求,還必須將信號送后級調理電路處理,經放大和衰減再通過射頻傳輸器把差分信號耦合成單端信號,最后輸出符合要求的正弦波信號。信號源的內調制是通過對調制波計算采樣后,在CPLD+DSP控制下,由 FIFO循環送數至DDS中實現的。外調制是通過ADC采用外調制信號,DSP測量外調制信號的頻率幅度, 再以內調制方式處理而實現的。內外調幅功能, 也可以通過乘法器AD835實現。數字調制功能由DSP+CPLD控制AD9854實現。

3.關鍵技術的實現

3.1芯片的操作與控制方法

AD9854提供了串行和并行兩種控制方式,為了滿足豐富的調制功能,需要對芯片進行高速的復雜控制,所以使用8位并行控制方式是合理的。并行接口有8位數據線和6位地址線,內部寄存器共40個,地址范圍00h~27h。其中1Dh~20h是控制寄存器,其他都是數據寄存器。系統僅要考慮對AD9854寫操作,按照寫時序關系,寫數據進入片內緩沖寄存器中,然后只有當數據更新管腳(pin20)出現正脈沖后(芯片工作在外部數據更新模式),數據由緩沖寄存器裝載至DDS核內。這時,DDS才以更新后的參數輸出信號。以三角形自動線性掃頻信號的產生為例,闡述對AD9854的操作步驟。

(1)復位DDS,即Master(pin71)保持10個以上系統時鐘周期的正脈沖。

(2)寫控制寄存器。設置工作模式、數據更新方式、鎖相環倍頻數、開啟和屏蔽相應的功能。因為是三角形自動線性掃頻,所以必須設置Triangle bit為高。

(3)寫數據寄存器。寫入掃頻的起始頻率和終止頻率, 設置掃頻步進和掃頻斜率。

(4)數據設置完成后,在數據更新管腳產生正脈沖,芯片開始掃頻,并不斷以終頻2初頻2終頻的方式循環。注意:掃頻開始時可以在FSK data管腳(pin29)產生正脈沖, 以決定從終頻還是從初頻開始掃頻。

3.2多種調制的實現方法

AD 9854片內可選5 種基本工作模式, 利用芯片提供的功能模塊, 配合DSP、CPLD和FIFO(first in first out) 可以實現功能擴展。

(1)數字調制

AD 9854 可以方便地實現二進制FSK和PSK。芯片提供了基帶數據輸入管腳(pin29),直接由該管腳的高低電平選擇2個不同的頻率和相位來實現FSK和PSK。M FSK M PSK的實現必須由用戶根據數據符號寬度的定時控制多個頻率或相位的切換。多種形式的掃頻功能也是由片內硬件實現的,詳細操作方法與§2.1中三角形掃頻例子相同。

(2)模擬調制

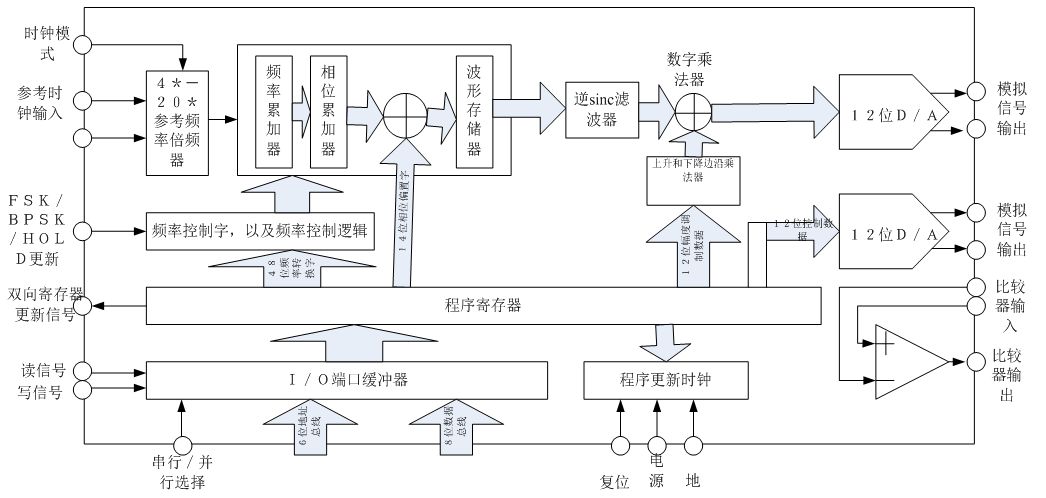

DSP通過對調幅波和調頻波的計算量化,將頻率字或幅度字按時序的先后關系依次存入FIFO中。在CPLD的作用下,FIFO不斷循環地向DDS傳送數據。如圖3所示,DSP將地址線連接在CPLD上,通過CPLD中的邏輯關系確定FIFO在IO口上的地址。DSP的低14位數據線和FIFO低14位數據線相連,則DSP送FIFO的14位數據按低8位數據,高6位地址排列。所以FIFO低8位數據線連接DDS的并行口數據線,FIFO高6位數據線連接DDS的并行口地址線,按照CPLD提供的讀寫時鐘信號傳送數據。DSP的CL Kout引腳接CPLD的GCLK引腳,提供全局工作時鐘。CPLD通過用戶IO引腳為FIFO和DDS提供相同的讀寫時鐘,實現器件間的時序同步。CPLD控制時序,不斷將FIFO中的數據循環送入DDS中,按周期刷新UPdata管腳以完成模擬調試。模擬調制的關鍵是CPLD協調FIFO和DDS的時序。調頻波和調幅波的頻率可以設置,則其頻率變化時,需要插入的等待周期就不同,即CPLD所控制的FIFO讀時鐘和DDS并行口寫時鐘都要隨調制波頻率的變化而變化。實現方法是DSP的數據線與地址線連接CPLD的IO口,在CPLD中設置一個計數值可變的計數器,計數器的輸出端通過CPLD的IO口連接FIFO讀時鐘和DDS并行口寫時鐘。計數器的計數值就決定了輸出時鐘頻率,這個值是DSP根據調制波頻率計算后由IO尋址方式送入CPLD的。

圖3 模擬調制的實現

3.3其他擴展功能方法

(1)正交信號的產生

AD9854有2個高速DAC,輸出信號的頻率、幅度和相位都可以獨立調節。只要使相位寄存器中預置值相差90°,則2路輸出信號相位差為90°,正交信號便產生。這樣信號源可為正交調制提供載波。

(2)脈寬可控的脈沖信號的產生

AD9854的I支路信號經低通濾波后作為內部高速比較器的負端輸入信號,Q支路信號經低通濾波后,作為比較器的正端輸入信號。通過設置DAC的輸入改變比較電平,控制脈沖寬度的變化,脈沖信號的頻率由頻率控制字1確定。

4.測試結果和分析

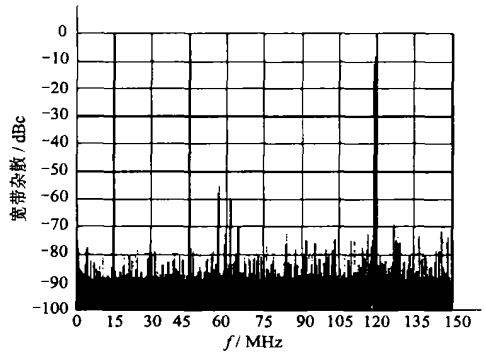

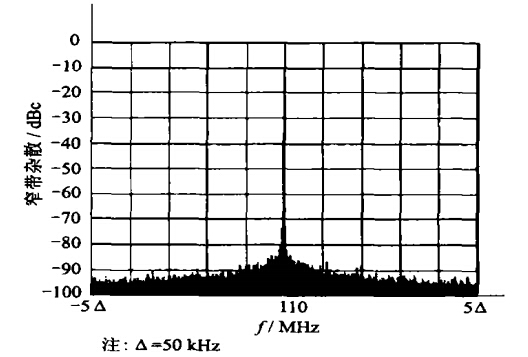

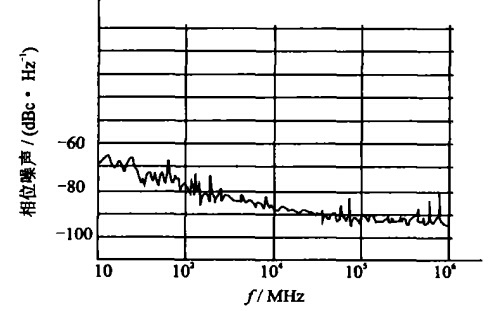

系統在確定了硬件結構后,精心設計硬件電路,完成系統調試和功能測試。測試樣機達到的主要性能指標,如表2 所示。測試結果與表1中參數對比,可以看出信號源輸出信號的頻率、電平、噪聲電平等主要性能指標完全達到要求。對整個頻率范圍內輸出信號的雜散性能,使用了頻譜分析儀A T 5011 進行測試,測試結果如圖4~6所示。圖4是輸出110M H z波形的寬帶雜散性能,其值優于40 dBc。圖5是輸出110 M H z 波形的窄帶雜散性能,其值在±250 kH z范圍內優于75 dBc。圖6是輸出110M H z 波形的相位噪聲,測量得到在偏離中心頻率1Hz處相位噪聲為- 80 dBc H z,當偏 10 H z 時,相位噪聲下降為- 60 dBc H z,之后隨偏離頻率變大,相位噪聲逐漸減小。測試結果表明,主要技術指標達到性能要求,進一步在電源設計、隔離電路設計和低通濾波器設計等方面進行改進, 還可以減少相位噪聲改善雜散性能。

表2 信號源樣機測試的性能指標

圖4 輸出信號110M Hz 時的寬帶雜散

圖5 輸出信號110M Hz 時的窄帶雜散

圖6 輸出信號110M Hz 時的相位噪聲

結語

基于AD9854的多功能信號源能靈活、方便地實現多種模擬調制和數字調制。系統最大限度地挖掘了AD9854的潛力,將數字信號處理器、可編程邏輯器件和先進先出存儲器與AD9854緊密結合, 輸出正弦信號的最高頻率為110M H z、諧波失真小于- 30 dBc。能夠完成調幅、調頻和頻移鍵控等調制功能。并通過了分析和實際測試結果表明,以DDS為核心構造多功能信號源的有效途徑。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹