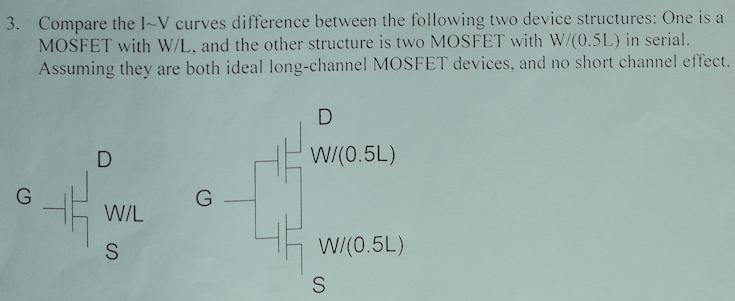

MOS管串聯(lián)

I-V曲線本來應(yīng)該一樣,但是由于effL,PSE的存在,以及間接導(dǎo)致的DIBL,都會讓這兩個(gè)曲線有區(qū)別

長溝道器件,兩者近似。短溝道器件差別大。

其實(shí)單純從W/L上考慮應(yīng)該是沒有區(qū)別的。

使用兩個(gè)(或多個(gè))串聯(lián),提高L。

我認(rèn)為好處如下:

正如二樓所說,避免使用倒比管(W/L遠(yuǎn)小于1時(shí));

通過拆分為多個(gè)管子串聯(lián)時(shí),在layout上容易布局、匹配;

串聯(lián)時(shí),如果SD電壓降低,一個(gè)管子進(jìn)入線性區(qū),但可保證另外一個(gè)工作在飽和區(qū)。

單純從w/l考慮,也應(yīng)該考慮背柵效應(yīng)的影響

低功耗中常用到

兩個(gè)nmos管串聯(lián)下面的mos管為什么下面的一直在線性區(qū) ?

上面的NMOS如果要開啟,那么它的G必然比S要高出VT0;

那么下面的NMOS的G必然比D要低于一個(gè)VT0(兩個(gè)管子的G電位一樣,上面的S就是下面的D);

那么下面的管子不就在線性區(qū)域嗎!

那么當(dāng)有電流I流過這2個(gè)NMOS時(shí),下面管子M1的Vgs1 〉上面管子M2的Vgs2 (因?yàn)閂ds1〉0),要保證I1=I2,則必須是M1在線形區(qū),M2飽和區(qū)。

并聯(lián)相當(dāng)于增加W,而串聯(lián)是不是增加L?

串聯(lián)是不是要一個(gè)管子的源極接另一個(gè)管子的漏極,而它們的柵極要連在一起,是應(yīng)該

這樣接嗎? 但如果我把兩個(gè)串聯(lián)后的管子再連成二極管負(fù)載的形式,其中一個(gè)管子總工作在線性區(qū)(因?yàn)関gs太大,而vds過小),不能保證一個(gè)管子在恒流區(qū),這樣用可以嗎,能相當(dāng)于增加了L嗎?

并聯(lián)相當(dāng)于增加W,而串聯(lián)是不是增加L?

是,如果sub接source的話

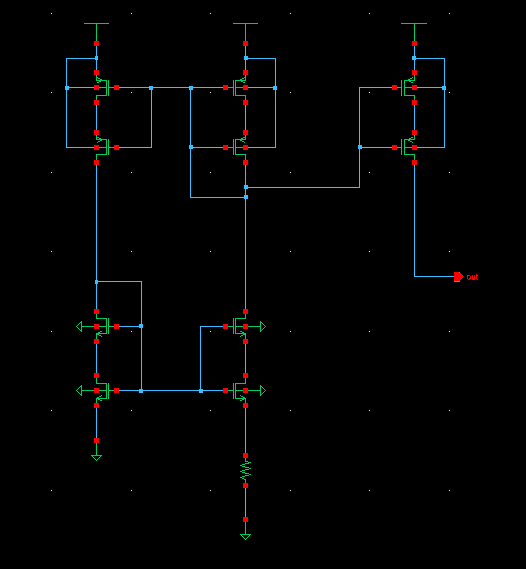

這應(yīng)該是電流鏡電路吧,中間的管子應(yīng)該比靠近電源和地的管子要寬得多吧? 這樣的話主意是使中間管子的柵源電壓約等于閾值電壓,左右兩路靠近電源和地的管子的柵漏電壓就被clip一個(gè)閾值電壓的值處,使左右兩路漏端電壓較為精確匹配,同時(shí)也可以使輸出擺幅最大化。

也可看成是由靠近電源的管子引入了一個(gè)源級負(fù)反饋,是電流匹配更好,PSRR也更好

想請問一下:假如兩個(gè)10u/5u+10u/2.5u串接同單獨(dú)的一個(gè)10u/7.5u管子做電流鏡,有區(qū)別嗎?我覺得表面上靠近電源和地的管子漏端電壓被嵌住了,但也不排除某一個(gè)管子進(jìn)入線性區(qū),匹配同樣不好!所以兩個(gè)管子串聯(lián)跟相應(yīng)地增加一個(gè)管子的L效果沒什么區(qū)別,個(gè)人看法請指正

靠近vdd的pmos管子如果Vg-Vd的絕對值為Vth的話,那就是處于臨界飽和了,再下面的管子飽和否我覺得比較起來沒那么重要。其實(shí)就算處于線性區(qū)同時(shí)match Vg和Vd的我也見過,扯遠(yuǎn)了。疊著的兩個(gè)管子合起來的話l大些,管子的match好些,但你不能牽著Vd,哪個(gè)更match些好難說, 但如果管子上了一定的尺寸后我相信match Vd會更好些

很簡單,共源共柵結(jié)構(gòu)的作用就是隔離,

使得漏端電與輸出隔離,減小溝長調(diào)制產(chǎn)生的失配

這是self cascode的current mirror

利用self cascode降低channel length modulation effect

如此接法mos將等效為(W/L)equal=1/[(L/W)1+(L/W)2]

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹