時鐘信號衰減會增加抖動,因此對驅動器輸出的端接很重要。為了避免抖動和時鐘質量降低的不利影響,需要使用恰當的信號端接方法。

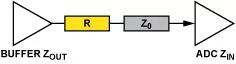

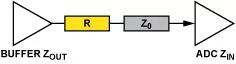

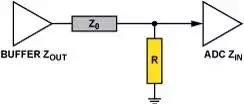

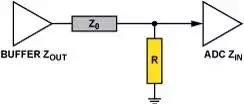

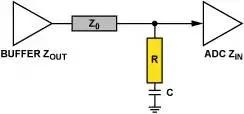

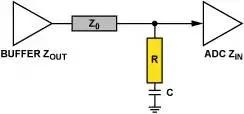

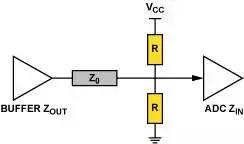

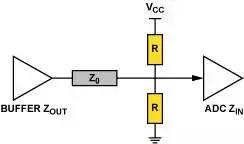

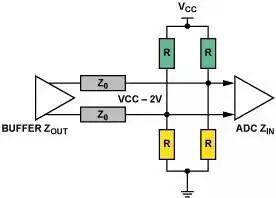

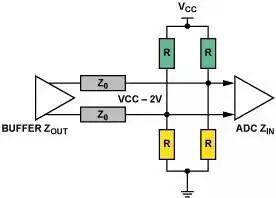

Z0是傳輸線的阻抗;

ZOUT 是驅動器的輸出阻抗,

ZIN 是接收器的輸入阻抗。

PS:這里僅顯示CMOS和PECL/LVPECL電路。

串行端接

實際上,因為阻抗會隨頻率動態變化,難以達到阻抗匹配,所以緩沖器輸出端可以省去電阻(R)。

優勢:

低功耗解決方案(沒有對地的吸電流)

很容易計算R的值 R (Z0 – ZOUT).

弱點:

上升/下降時間受RC電路的影響,增加抖動

只對低頻信號有效

備注:

CMOS驅動器

不適合高頻時鐘CMOS drivers信號

適合低頻時鐘信號和非常短的走線

下拉電阻

CMOS

優勢:非常簡單(R = Z0)

弱點:高功耗

備注:不推薦

LVPECL

優勢:

簡單的3電阻解決方案。

就節能而言稍好一點,相對于4電阻端接來說節省一個電阻。

備注:推薦。端接電阻盡可能靠近PECL接收器放置。

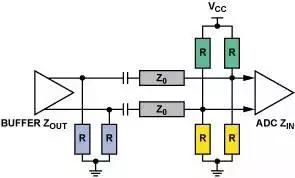

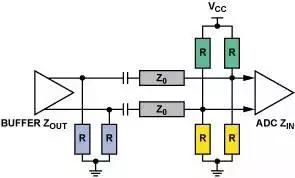

交流端接

CMOS

優勢:沒有直流功耗。

備注:為避免較高功耗,C應該很小,但也不能太小而導致吸電流。

LVPECL

優勢:交流耦合允許調整偏置電壓。避免電路兩端之間的能量流動。

弱點:交流耦合只推薦用于平衡信號(50%占空比的時鐘信號)。

備注:交流耦合電容的ESR值和容值應該很低。

電阻橋

CMOS

優勢:功耗實現合理的權衡取舍。

弱點:單端時鐘用兩個器件。

LVPECL

弱點:差分輸出邏輯用4個外部器件。

備注:3.3V LVPECL驅動器廣泛應用端接。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹