隨著移動通信技術的發展,射頻(RF)電路的研究引起了廣泛的重視。采用標準CMOS工藝實現壓控振蕩器(VCO),是實現RF CMOS集成收發機的關鍵。過去的VCO電路大多采用反向偏壓的變容二極管作為壓控器件,然而在用實際工藝實現電路時,會發現變容二極管的品質因數通常都很小,這將影響到電路的性能。于是,人們便嘗試采用其它可以用CMOS工藝實現的器件來代替一般的變容二極管,MOS變容管便應運而生了。

MOS變容管

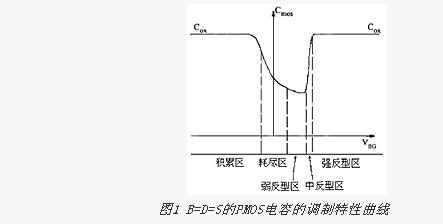

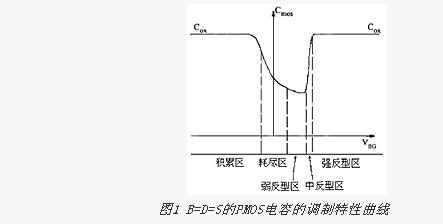

將MOS晶體管的漏,源和襯底短接便可成為一個簡單的MOS電容,其電容值隨柵極與襯底之間的電壓VBG變化而變化。在PMOS電容中,反型載流子溝道在VBG大于閾值電壓時建立,當VBG遠遠大于閾值電壓時,PMOS電容工作在強反型區域。另一方面,在柵電壓VG大于襯底電壓VB時,PMOS電容工作在積累區,此時柵氧化層與半導體之間的界面電壓為正且能使電子可以自由移動。這樣,在反型區和積累區的PMOS電容值Cmos等于Cox(氧化層電容)。

在強反型區和積累區之間還有三個工作區域:中反型區,弱反型區和耗盡區。這些工作區域中只有很少的移動載流子,使得Cmos電容值減小(比Cox小),此時的Cmos可以看成Cox和Cb與Ci的并聯電容串聯構成。Cb表示耗盡區域電容的閉環,而Ci與柵氧化層界面的空穴數量變化量相關。如果Cb(Ci)占主導地位,PMOS器件工作在耗盡(中反型)區;如果兩個電容都不占主導地位,PMOS器件工作在弱反型區。Cmos電容值隨VBG變化的曲線如圖1所示。

工作在強反型區的PMOS的溝道寄生電阻值可以由下式得出:

(1)

式中,W,L和kp分別是PMOS晶體管的寬度,長度和增益因子。值得注意的是,隨著VBG接近閾值電壓的,Rmos逐步增加,在VBG等于閾值電壓時Rmos為無限大。這個公式基于了簡單的PMOS模型,事實上,隨著空穴濃度的穩步減少,Rmos在整個中反型區會保持有限值。

反型與積累型MOS變容管

通過上面的分析,我們知道普通MOS變容管調諧特性是非單調的,目前有兩種方法可以獲得單調的調諧特性。

一種方法是確保晶體管在VG變化范圍大的情況下不進入積累區,這可通過將襯底與柵源結斷開而與電路中的直流電壓短接來完成(例如,電源電壓Vdd)。

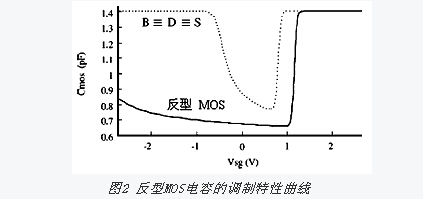

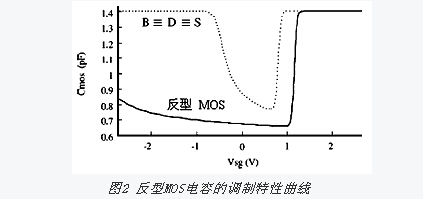

圖2是兩個相同尺寸MOS電容的Cmos-VSG特性曲線的相互對比。

很明顯反型MOS電容的調諧范圍要比普通MOS電容寬,前者只工作在強,中和弱反型區,而從不進入積累區。

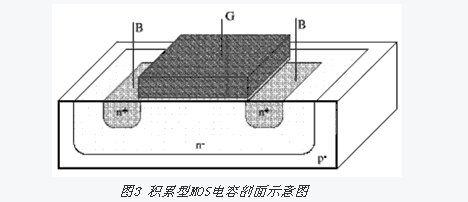

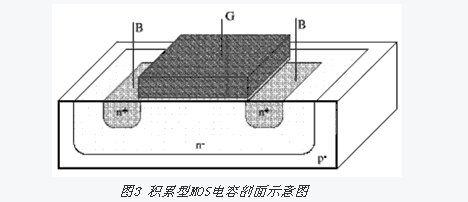

更好的方法是應用只工作在耗盡區和積累區的MOS器件,這樣會帶來更大的調諧范圍并且有更低的寄生電阻,即意味著更高的品質因數,原因是其耗盡區和積累區的電子是多子載流子,比空穴的遷移率高約三倍多。要得到一個積累型MOS電容,必須確保強反型區,中反型區和弱反型區被禁止,這就需要抑制任何空穴注入MOS的溝道。方法是將MOS器件中的漏源結的p+摻雜去掉,同時在原來漏源結的位置做n+摻雜的襯底接觸,如圖3所示。

這樣就將n阱的寄生電阻減少到。積累型MOS電容和普通MOS電容的調諧曲線如圖4所示。

可以看到積累型MOS電容良好的單調性。值得注意的是在設計積累型MOS電容的過程中沒有引入任何附加工藝流程。

設計與仿真結果

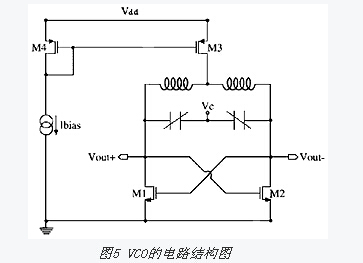

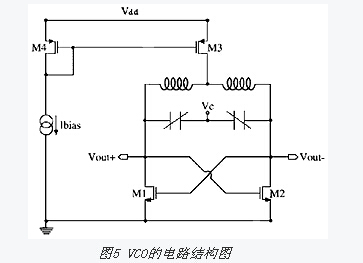

所采用的VCO電路結構如圖5所示。這是標準的對稱CMOS結構,兩個變容管對稱連接,減小了兩端振蕩時電位變化對變容管電容值的影響,提高了頻譜純度。為了保證匹配良好,電感要采用相同的雙電感對稱連接。此外,由于LC振蕩回路由兩個尺寸非常大的片內集成電感和兩個同樣有較大尺寸的積累型MOS變容管組成,較高的損耗使得品質因數不高,這就需要較大的負跨導來維持振蕩持續進行;并且等效負跨導的必須比維持等幅振蕩時所需要的跨導值大才能保證起振,所以兩對耦合晶體管需要設置較大的寬長比,但大的寬長比同時帶來較大的寄生效應,造成相位噪聲和調諧范圍受到影響,終在底端用兩個NMOS晶體管形成負電阻以補償VCO的損耗。根據小信號模型分析,忽略各種寄生及高階效應,可以估算得到等效負電阻RG的大小為(設兩個有源器件跨導分別為gM1,gM2):

(2)

頂端的PMOS晶體管提供偏置電流,這種結構所需的電源電壓很低。

整個設計基于TSMC的0.35μm鍺硅射頻工藝模型PDK,共有三層金屬。其中,電感為平面螺旋八邊形,由頂層金屬繞制而成。選取電感值為0.6nH,那么在振蕩頻率選定的情況下可以確定總的電容大小。構成LC振蕩回路里的電容成份有電感的寄生電容(很小),NMOS晶體管的漏-襯底電容,柵-漏電容,柵-源電容和重要的積累型MOS電容。在保證起振的情況下,為了獲得更大的調諧范圍,一項所占比例必須盡可能大。

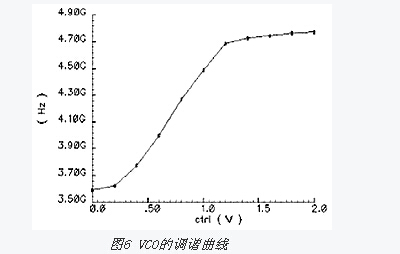

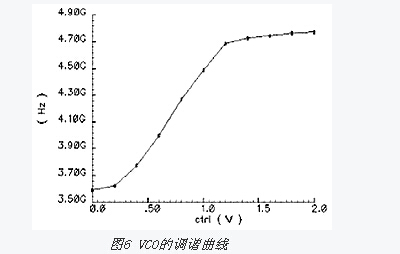

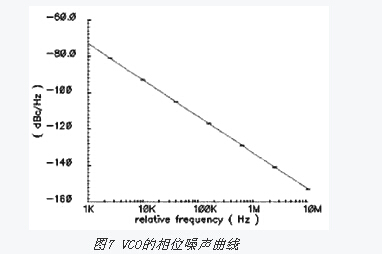

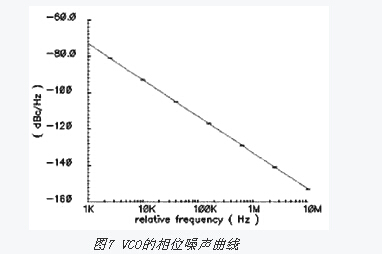

采用的電源電壓為1.5V,功耗約為10mW。用Cadence平臺下的SpectreRF進行仿真,得到的調諧曲線如圖6所示。控制電壓在0~2V變化時,振蕩頻率在3.59~4.77GHz間變化,中心頻率為4.18GHz,調諧范圍約為28%。中心頻率處的相位噪聲曲線如圖7所示,此時的控制電壓為0.75V,對應偏移量600kHz的相位噪聲為-128dB/Hz。

當控制電壓由0.75V變到2V時,振蕩頻率變為4.77GHz,相位噪聲變為 -135dB/Hz,降低了7dB。這是由兩個方面的原因引起的,首先是由于LC振蕩回路總的電容減小,振蕩頻率增加,這就減小了要維持振蕩所需的負跨導,但因為兩個NMOS晶體管提供的負跨導幾乎不變,所以就使得穩定振蕩幅度增加,相位噪聲減小。另外一方面是源于此過程中積累型MOS電容的溝道寄生電阻會隨著電壓升高而變小,從而降低了損耗,降低了相位噪聲。

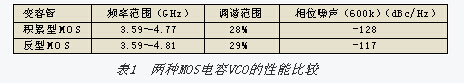

與采用反型MOS變容管設計的VCO比較,由于電子具有較高的遷移率,使得積累型MOS電容的溝道寄生電阻比反型MOS電容要低,即意味著積累型MOS電容具有較高的品質因數,導致了VCO整體性能有所提高,特別是相位噪聲有所減少。比較結果如表1所示。考慮到工藝和功耗等因素,采用積累型MOS電容有更大的優勢。

結論

基于0.35μm工藝,考慮低壓和低功耗,設計了一個工作頻率為4.2GHz的VCO,并在該電路中分別采用積累型MOS電容和反型MOS電容進行調諧。仿真結果表明,兩種VCO調諧范圍與中心頻率幾乎相同,在功耗約為10mW的情況下,積累型MOS調諧的VCO表現出更好的相位噪聲性能。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹