電機(jī)驅(qū)動(dòng) Motor drive 是組裝在膠片式照相機(jī)內(nèi)的微型電機(jī)或彈簧及其附件的總稱(chēng),借助微型電機(jī)自動(dòng)地卷取膠片,大多是指 35 毫米單鏡頭反光相機(jī)所用的。

01 供電電路原理

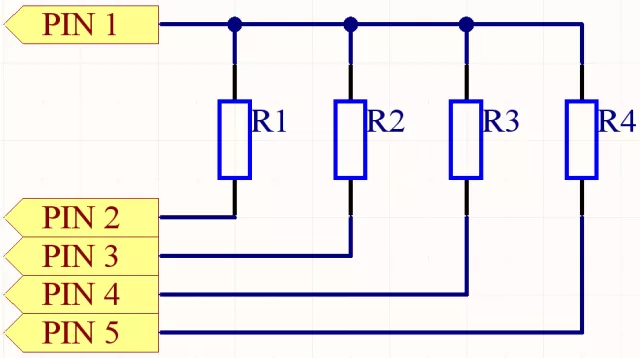

供電部分原理圖如圖 1-1 所示:

圖 1-1

從圖 1-1 中可知道供電有+5V、+3.3V、+1.5V 三種,其中每個(gè)電源均有 0.1µF 的旁路電容,將電源中的高頻串?dāng)_旁路到地,防止高頻信號(hào)通過(guò)電源串?dāng)_到其它模塊中。同時(shí)還能將電源本身的工頻干擾濾除。

值得注意的是:在布線(xiàn)的時(shí)候,經(jīng)退藕電容退藕后的電源輸出點(diǎn)應(yīng)該盡量緊靠芯片的電源引腳進(jìn)行供電,過(guò)長(zhǎng)的引線(xiàn)有可能重新變成干擾接收天線(xiàn),導(dǎo)致退藕效果消失。如果無(wú)法讓每個(gè)退藕后的電源輸出點(diǎn)均緊靠芯片的電源引腳,那么可以采用分別退藕的方法,即分別盡量緊靠每個(gè)芯片的電源引腳點(diǎn)接入退藕電容進(jìn)行退藕,這也解釋了為什么圖 1-1 的 3.3V 電源有兩個(gè)退藕輸出點(diǎn)。

02、電機(jī)驅(qū)動(dòng)電路原理

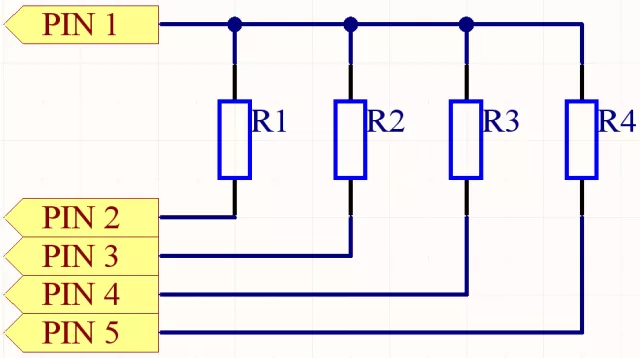

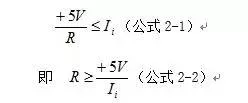

電機(jī)驅(qū)動(dòng)電路原理如圖 2-1 所示:

圖 2-1

圖 2-1 中 Header 4X2 為 4 排 2 列插針,F(xiàn)M0~3 為 FPGA 芯片 I/O 輸出口,加入的插針給予一個(gè)可動(dòng)的機(jī)制,在需要使用時(shí)才用跳線(xiàn)帽進(jìn)行相連,提高 I/O 口的使用效率。RES5 是五端口排阻,內(nèi)部集成了 4 個(gè)等阻值且一端公共連接的電阻,PIN 1 是公共端,PIN2~5 為排阻的輸出端,排阻原理圖如圖 2-2 所示:

圖 2-2

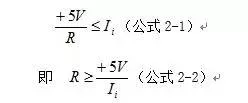

該排阻公共端接電源,即上拉電阻形式,作用是增強(qiáng) FPGA 芯片 I/O 口(以下簡(jiǎn)稱(chēng) I/O 口)的驅(qū)動(dòng)能力,實(shí)際上就是增加 I/O 輸出高電平時(shí)輸出電流的大小。當(dāng) I/O 輸出高電平時(shí),+5V 電源經(jīng)排阻與 IN1~4 相連,相當(dāng)于為 I/O 提供一個(gè)額外的電流輸出源,從而提高驅(qū)動(dòng)能力。當(dāng) I/O 輸出低電平時(shí),可將 I/O 近似看做接地,而 IN1~4 因與 I/O 由導(dǎo)線(xiàn)直接相連,因此直接接受了 I/O 的低電平輸出信號(hào)。此時(shí),+5V 電源經(jīng)排阻 R、I/O 內(nèi)部電路(電阻近似為零)后接地,因此該路的電流不能大于 I/O 的拉電流(Ii)最大值,有公式 2-1:

由公式 2-2 可以得出排阻的取值范圍。

該上拉電阻除了提高驅(qū)動(dòng)能力外,還有一個(gè)作用,就是進(jìn)行電平轉(zhuǎn)換。經(jīng)查,ULN2003 的接口邏輯為:5V-TTL, 5V-CMOS 邏輯。而在 3.3V 供電的情況下,I/O 口可以提供 3.3V-LVTTL,3.3V-LVCMOS,3.3V-PCI 和 SSTL-3 接口邏輯電平。因此,需要外接 5V 的上拉電阻將 I/O 電平規(guī)格變成 5V 電平邏輯。

芯片 ULN2003 內(nèi)部集成 7 組達(dá)林頓管,專(zhuān)門(mén)用于提高驅(qū)動(dòng)電流,芯片引腳間邏輯如圖 2-3 所示:

圖 2-3

圖 2-4

由于 I/O 電流遠(yuǎn)遠(yuǎn)不足以驅(qū)動(dòng)電機(jī),因此需要外接該芯片驅(qū)動(dòng)電機(jī),ULN2003 內(nèi)部集成的達(dá)林頓管電路如圖 2-4 所示。達(dá)林頓管的形式具有將弱點(diǎn)信號(hào)轉(zhuǎn)化成強(qiáng)電信號(hào)的特點(diǎn),I/O 電平邏輯從 PIN IN 輸入,通過(guò)達(dá)林頓管控制 PIN 9(COMMON)端輸入的強(qiáng)電信號(hào)按照 I/O 信號(hào)規(guī)律變化。值得注意的是:ULN2003 輸出邏輯將與輸入邏輯相反,編程時(shí)應(yīng)該注意該特點(diǎn)。

RES6 是六端口排阻,內(nèi)部集成了 5 個(gè)等阻值且一端公共連接的電阻,PIN 1 是公共端,PIN2~6 為排阻的輸出端,原理圖與接法說(shuō)明可參考上述圖 2-2,排阻取值范圍計(jì)算參見(jiàn)公式 2-2,此處不再贅述。值得注意的是:RES6 的 PIN 1 與 PIN 2 相連,是因?yàn)槎喑隽艘粋€(gè)不使用的電阻,為了避免 PIN 2 懸空,因此將 PIN 2 與 PIN 1(公共端)相連,即 PIN 2 對(duì)應(yīng)的電阻被短路,從而既避免的懸空的引腳,又能使該電阻失效。

03 電機(jī)指示燈電路原理

電機(jī)指示燈電路如圖 3-1 所示:

圖 3-1

電機(jī)部分指示燈用于指示各路信號(hào)的邏輯電平狀態(tài),其中 R106~109 為限流電阻,防止發(fā)光二極管因電流過(guò)大燒毀。值得注意的是:該指示燈的發(fā)光二極管接成共陽(yáng)極,由 M0~3 信號(hào)端口產(chǎn)生低電平點(diǎn)亮對(duì)應(yīng)的二極管,而 ULN2003 的 OUT 與 IN 邏輯電平相反,因此對(duì)于 I/O 口 FM0~3 來(lái)說(shuō),輸出高電平就能點(diǎn)亮對(duì)應(yīng)的發(fā)光二極管,例如:FM0 輸出高電平,則對(duì)應(yīng) LD17 點(diǎn)亮,編程時(shí)應(yīng)注意此電路將 I/O 實(shí)際邏輯反相了兩次,對(duì)應(yīng)關(guān)系為 I/O 口輸出哪路高電平則對(duì)應(yīng)點(diǎn)亮哪路指示燈。

04 時(shí)鐘電路原理

時(shí)鐘電路如圖 4-1 所示:

圖 4-1

采用 50Mhz 有源晶振產(chǎn)生時(shí)鐘信號(hào),接法采用有源晶振的典型接法:PIN 1 懸空,PIN 2 接地,PIN 3 輸出時(shí)鐘信號(hào),PIN 4 接電源。由于 FPGA 的 I/O 供電為 3.3V,而時(shí)鐘電路產(chǎn)生的時(shí)鐘信號(hào)要由 I/O 口接收,因此時(shí)鐘信號(hào)最大值不能超過(guò) 3.3V,故時(shí)鐘電路電源采用 3.3V 供電。

05FPGA 部分電路原理

FPGA 部分電路原理圖如圖 5-1 所示:

圖 5-1

Header 18X2 為 18 排 2 列排陣,兩組排陣分別與 PIN 口、3.3V 電源、數(shù)字地相連,提供了可動(dòng)的機(jī)制,使得 PIN 口可根據(jù)需要用排線(xiàn)與目標(biāo)相連,達(dá)到信號(hào)傳輸?shù)哪康摹6?3.3V 電源以及數(shù)字地針口則可以根據(jù)需要,用排線(xiàn)為目標(biāo)提供邏輯高電平或邏輯低電平。

U21D 為 FPGA 芯片的時(shí)鐘信號(hào)接收部分,通過(guò)網(wǎng)絡(luò)標(biāo)號(hào)“CLK0~3”與對(duì)應(yīng)的時(shí)鐘信號(hào)端口相連。

U21C 為 FPGA 芯片的供電及接地部分,含有“GND”字樣的是“地”端口,與數(shù)字地相連,VCCIO1~4 為 I/O 口供電端口,采用 3.3V 電源供電,通過(guò)網(wǎng)絡(luò)標(biāo)號(hào)“+3.3V”與 3.3V 電源端口相連。VCCA_PLL1、VCCA_PLL2、VCCINT 為內(nèi)部運(yùn)算器和輸入緩沖區(qū)的供電端口,采用 1.5V 電源供電,通過(guò)網(wǎng)絡(luò)標(biāo)號(hào)“+1.5V”與 1.5V 電源端口相連。

U21B 為 JTAG 與 AS 下載部分,TMS、TCK、TD1、TD0 分別為 JATAG 下載方式的模式選擇端、時(shí)鐘信號(hào)端、數(shù)據(jù)輸入端、數(shù)據(jù)輸出端。DATA0 為 AS 下載的數(shù)據(jù)端口,MSEL0、MSEL1、nCE、nCEO、CONF_ DONE、nCONFIG、nSTATUS 端口按照典型接法相連。值得注意的是:無(wú)論 AS 還是 JTAG 都是通過(guò) JTAG 標(biāo)準(zhǔn)通訊,AS 下載一般是下載 POF 到 PROM(flash)里,重新上電仍然可以加載,JTAG 下載是通過(guò) JTAG 口將 sof 文件直接下載到 FPGA 內(nèi),一般是臨時(shí)調(diào)試用的,掉電就丟失了。

U22 是電可擦除 ROM,用于存放 AS 下載后的數(shù)據(jù),使得 FPGA 的程序段掉電也能得以保存,DATA 端是數(shù)據(jù)讀取端,用于讀取 ROM 內(nèi)數(shù)據(jù)。DCLK 為時(shí)鐘端口,用于接收時(shí)鐘信號(hào)進(jìn)行同步傳輸。nCS 是片選端口,用于接收片選信號(hào)表示對(duì)該芯片進(jìn)行通訊。ASDI 為 AS 下載數(shù)據(jù)輸入端,用于接收 AS 下載數(shù)據(jù)。VCC 與 GND 分別為電源端口與地端口,分別接 3.3V 與數(shù)字地。

烜芯微專(zhuān)業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠(chǎng)直銷(xiāo)省20%,4000家電路電器生產(chǎn)企業(yè)選用,專(zhuān)業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷(xiāo)售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

烜芯微專(zhuān)業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠(chǎng)直銷(xiāo)省20%,4000家電路電器生產(chǎn)企業(yè)選用,專(zhuān)業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷(xiāo)售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹