1總體方案設計

線陣 CCD 一般不能直接在測量裝置中使用,因此 CCD 驅動信號的產生及輸出信號的處理是設計高精度、高可靠性和高性價比線陣 CCD 驅動模塊的關鍵。

傳統驅動 CCD 的設計方法使 CCD 的工作頻率較慢,信號輸出噪聲增大,不利于提高信噪比,不能應用于要求快速測量的場合。而用可編程邏輯器件 CPLD 進行驅動,則可提高脈沖信號相位關系的精度,以及提供給 CCD 驅動脈沖信號的頻率,而且調試容易、靈活性高。目前,在工業技術中,多采用基于 CPLD 的驅動電路實現線陣 CCD 的驅動。系統框圖如圖 1 所示。

圖 1 基于 CPLD 的線陣 CCD 的驅動電路

2 硬件設計

2. 1 CPLD 的硬件電路的設計

以 CPLD( Complex Programmable Logic Device) 器件為核心,設計線陣 CCD 的驅動電路。然后在其基礎上擴展,選擇其他元器件,設計出與其相配套的電路部分,經調試后組成硬件系統。

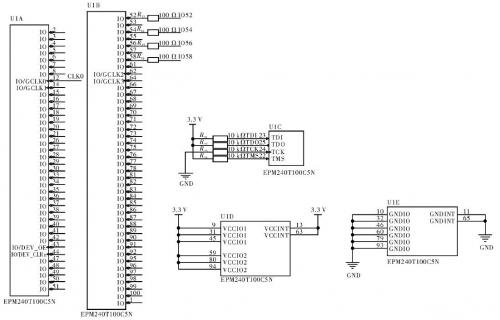

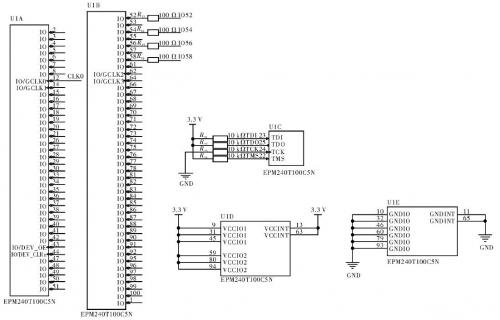

CPLD 的電路由 5 部分組成, 有源晶振向 EPM240T100C5N 的 U1A 的 IO/GCLK0 口輸入時鐘脈沖 CLK0,提供了 CPLD 工作的時鐘脈沖,因為時序邏輯的需要。U1C 從 JTAG 端口中下載程序,U1B 的 52、54、56、58 口輸出脈沖信號。U1D 管腳接 3. 3 V 電壓,U1E 管腳接地。電路原理如圖 2 所示。

圖 2 CPLD 的電路原理圖

2. 2 DC /DC 模塊的設計

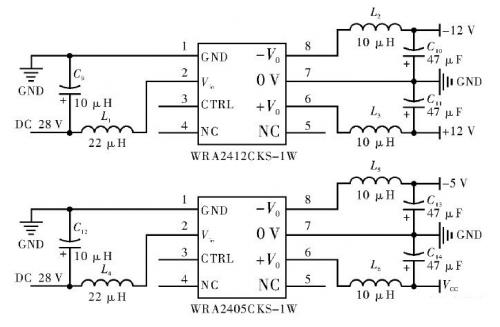

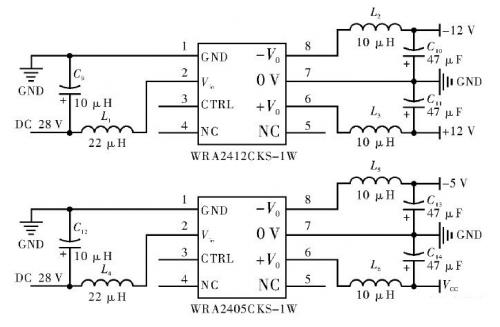

為得到 CPLD 所需的電壓,外接電源需要經過 DC /DC 模塊進行轉換。為進一步減少輸出紋波,可在輸入輸出端連接一個 LC 濾波網絡,電路原理如圖 3 所示。

圖 3 DC/DC 模塊的電路原理圖設計

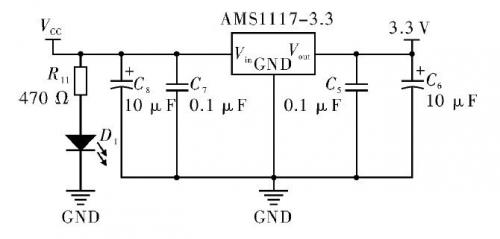

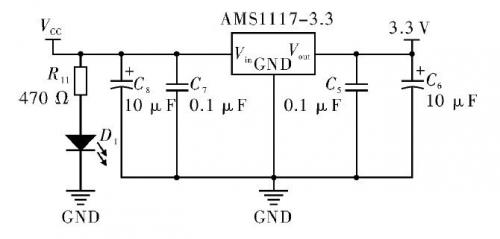

2. 3 穩壓模塊的電路設計

由 DC /DC 模塊轉換的直流電壓,經過一個 R11 電阻和一個發光二極管接地,發光二極管指示燈,然后從 AMS 芯片的 Vin 端輸入,進入到芯片的內部,經過一系列的計算,從 Vout 輸出 3. 3 V 電壓,GND 端端口接地。為消除交流電的紋波,電路采用電容濾波,分別用 0. 1 μF 的極性電容和 10 μF 的非極性電容組成一個電容濾波網絡。電路原理如圖 4 所示。

圖 4 穩壓模塊的電路設計

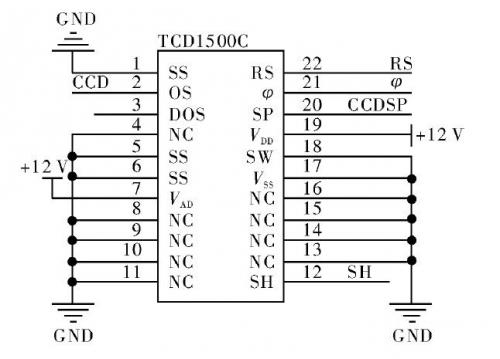

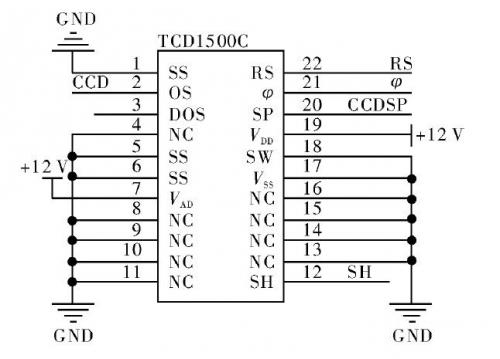

2. 4 CCD 電路設計

CCD 電路采用 TCD1500C,它是一個高靈敏度、低暗流、5340 像元的線陣圖像傳感器。其像敏單元大小是 7 μm × 7 μm × 7 μm,相鄰像元中心距 7 μm,像元總長 37. 38 mm. 該傳感器可用于傳真、圖像掃描和 OCR.TCD1500C 的測量精度和分辨率都很高,并且只需 4 路驅動信號: SH、φ、RS、SP。電路原理如圖 5 所示。

圖 5 CCD 模塊電路原理圖

2. 5 電平轉換的電路設計

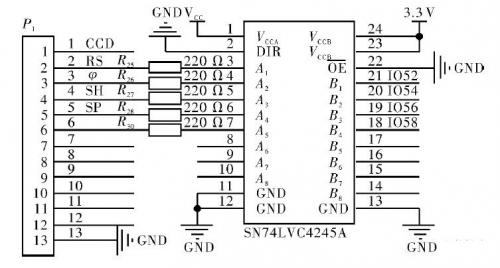

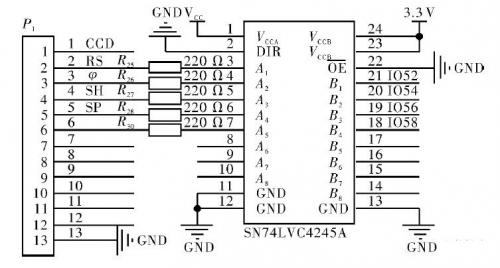

由于 CPLD 輸出的驅動脈沖電壓為 3. 3 V,而 CCD 工作所需的驅動脈沖為 5 V,所以需要在 CPLD 和 CCD 之間加入一個電平轉換電路。電路原理如圖 6 所示。

圖 6 電平轉換的電路原理圖

3 軟件設計

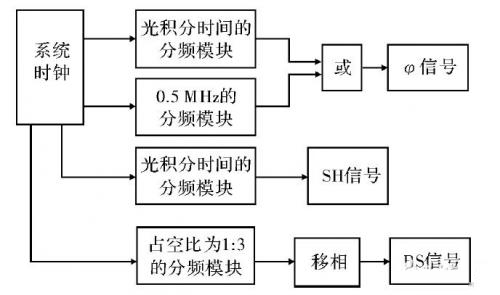

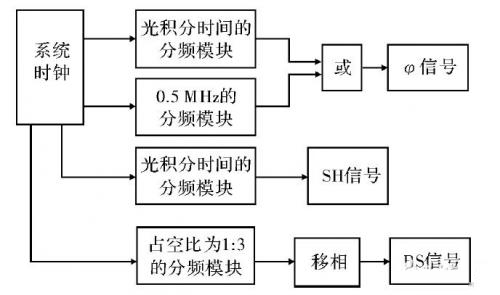

系統軟件采用 Verilog HDL 硬件描述語言,按照模塊化的思路設計,將要完成的任務分成為多個模塊,每個模塊由一個或多個子函數完成。這樣能使設計思路清晰、移植性強,在調試軟件時容易發現和改正錯誤,降低了軟件調試的難度。程序中盡量減少子函數之間的相互嵌套調用,這樣可以減少任務之間的等待時間,提高系統處理任務的能力[7 - 8]。主程序如圖 7 所示。

圖 7 主程序流程圖

SH 是一個光積分信號,SH 信號的相鄰兩個脈沖之間的時間間隔代表了積分時間的長短。光積分時間為 5 416 個 RS 周期,對系統時鐘進行光積分的分頻,實現了 SH 信號脈沖。在光積分階段,SH 為低電平,它使存儲柵和模擬移位寄存器隔離,不會發生電荷轉移。時鐘脈沖φ 為典型值 0. 5 MHz 時,占空比為 50%,占空比是指高電平在一個周期內所占的時間比率。它是 SH 信號和占空比為 50%的一個 0. 5 MHz 的脈沖信號疊加,所以 0. 5 MHz 的信號和 SH 信號通過一個或門,就可以實現φ 信號; 輸出復位脈沖 RS 為 1 MHz,占空比 1∶ 3. 此外,RS 信號和 SH、φ 信號有一定的相位關系,通過一個移位寄存器移相,來實現 RS 脈沖信號。

4 仿真實驗

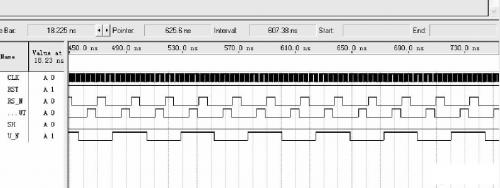

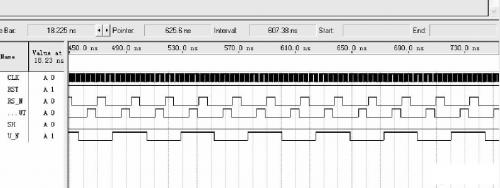

系統時鐘周期部分設置為 1 ns,正常工作時復位信號 RS 為高電平,然后對 RS、φ、SH 信號進行仿真,結果如圖 8 所示。

圖 8 QuartusⅡ仿真效果圖

5 結束語

研究的線陣 CCD 驅動電路主要是以 CPLD 為驅動中心而設計,這種方案減少了以往驅動電路的電路體積大、設計復雜、調試困難等缺點,增加了系統的穩定性、可靠性,集成度高且抗干擾能力強。通過對硬件和軟件大量的模擬實驗表明,文中所研究的線陣 CCD 驅動脈沖信號能夠滿足 CCD 工作所需的基本功能,達到了設計要求。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹