MOSFET擊穿電壓有哪幾種

場效應管的三極:源級(Source)S、漏級(Drain)D、柵級(Gate)G

(這里不講柵極GOX擊穿了啊,只針對MOSFET擊穿電壓漏極電壓擊穿)

先講測試條件,都是源柵襯底都是接地,然后掃描漏極電壓,直至Drain端電流達到1uA。所以從器件結構上看,它的漏電通道有三條:Drain(漏級)到source(源級)、Drain(漏級)到Bulk、Drain(漏級)到Gate(柵級)。

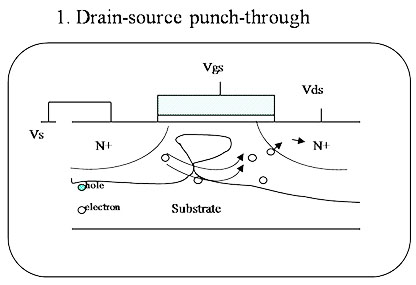

1)MOSFET擊穿電壓-Drain(漏極)->Source(源極)穿通擊穿

這個主要是Drain(漏極)加反偏電壓后,使得Drain(漏極)/Bulk的PN結耗盡區延展,當耗盡區碰到Source(源極)的時候,那源漏之間就不需要開啟就形成了通路,所以叫做穿通(punchthrough)。那如何防止穿通呢,這就要回到二極管反偏特性了,耗盡區寬度除了與電壓有關,還與兩邊的摻雜濃度有關,濃度越高可以抑制耗盡區寬度延展,所以flow里面有個防穿通注入(APT:AntiPunchThrough),記住它要打和well同type的specis。當然實際遇到WAT的BV跑了而且確定是從Source(源極)端走了,可能還要看是否PolyCD或Spacer寬度,或者LDD_IMP問題了,那如何排除呢這就要看你是否NMOS和PMOS都跑了POLYCD可以通過Poly相關的WAT來驗證。

對于穿通擊穿,有以下一些特征:

(1)穿通擊穿的擊穿點軟,擊穿過程中,電流有逐步增大的特征,這是因為耗盡層擴展較寬,產生電流較大。另一方面,耗盡層展寬大容易發生DIBL效應,使源襯底結正偏出現電流逐步增大的特征。

(2)穿通擊穿的軟擊穿點發生在源漏的耗盡層相接時,此時源端的載流子注入到耗盡層中,被耗盡層中的電場加速達到漏端,因此,穿通擊穿的電流也有急劇增大點,這個電流的急劇增大和雪崩擊穿時電流急劇增大不同,這時的電流相當于源襯底PN結正向導通時的電流,而雪崩擊穿時的電流主要為PN結反向擊穿時的雪崩電流,如不作限流,雪崩擊穿的電流要大。

(3)穿通擊穿一般不會出現破壞性擊穿。因為穿通擊穿場強沒有達到雪崩擊穿的場強,不會產生大量電子空穴對。

(4)穿通擊穿一般發生在溝道體內,溝道表面不容易發生穿通,這主要是由于溝道注入使表面濃度比濃度大造成,所以,對NMOS管一般都有防穿通注入。

(5)一般的,鳥嘴邊緣的濃度比溝道中間濃度大,所以穿通擊穿一般發生在溝道中間。

(6)多晶柵長度對穿通擊穿是有影響的,隨著柵長度增加,擊穿增大。而對雪崩擊穿,嚴格來說也有影響,但是沒有那么顯著。

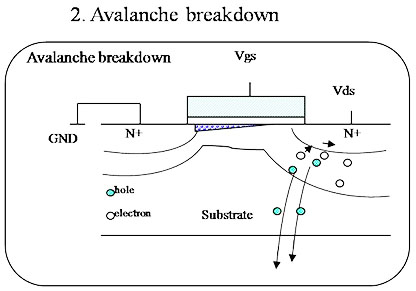

2)MOSFET擊穿電壓-Drain(漏極)->Bulk雪崩擊穿

這就單純是PN結雪崩擊穿了(**alancheBreakdown),主要是漏極反偏電壓下使得PN結耗盡區展寬,則反偏電場加在了PN結反偏上面,使得電子加速撞擊晶格產生新的電子空穴對(Electron-Holepair),然后電子繼續撞擊,如此雪崩倍增下去導致擊穿,所以這種擊穿的電流幾乎快速增大,I-Vcurve幾乎垂直上去,很容燒毀的。(這點和源漏穿通擊穿不一樣)

那如何改善這個junctionBV呢所以主要還是從PN結本身特性講起,肯定要降低耗盡區電場,防止碰撞產生電子空穴對,降低電壓肯定不行,那就只能增加耗盡區寬度了,所以要改變dopingprofile了,這就是為什么突變結(Abruptjunction)的擊穿電壓比緩變結(GradedJunction)的低。這就是學以致用,別人云亦云啊。

當然除了dopingprofile,還有就是doping濃度,濃度越大,耗盡區寬度越窄,所以電場強度越強,那肯定就降低擊穿電壓了。而且還有個規律是擊穿電壓通常是由低濃度的那邊濃度影響更大,因為那邊的耗盡區寬度大。公式是BV=K*(1/Na+1/Nb),從公式里也可以看出Na和Nb濃度如果差10倍,幾乎其中一個就可以忽略了。

那實際的process如果發現BV變小,并且確認是從junction走的,那好好查查你的Source(源極)/Drain(漏極)implant了

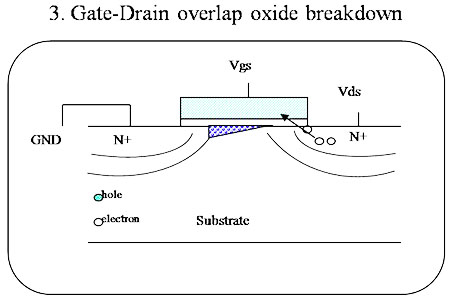

3)MOSFET擊穿電壓-Drain(漏極)->Gate(柵級)擊穿

這個主要是Drain(漏極)和Gate(柵級)之間的Overlap導致的柵極氧化層擊穿,這個有點類似GOX擊穿了,當然它更像Polyfinger的GOX擊穿了,所以他可能更carepolyprofile以及sidewalldamage了。當然這個Overlap還有個問題就是GIDL,這個也會貢獻Leakage使得BV降低。

上面講的就是MOSFET的擊穿的三個通道,通常BV的case以前兩種居多。

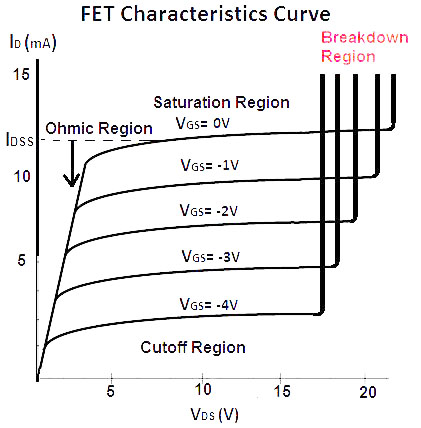

上面講的都是Off-state下的擊穿,也就是Gate(柵級)為0V的時候,但是有的時候Gate(柵級)開啟下Drain(漏極)加電壓過高也會導致擊穿的,我們稱之為On-state擊穿。這種情況尤其喜歡發生在Gate較低電壓時,或者管子剛剛開啟時,而且幾乎都是NMOS。所以我們通常WAT也會測試BVON,不要以為很奇怪,但是測試condition一定要注意,Gate(柵級)不是隨便加電壓的哦,必須是Vt附近的電壓。(本文開始我貼的那張圖,Vg越低時on-state擊穿越低)有可能是Snap-back導致的,只是測試機臺limitation無法測試出標準的snap-back曲線。另外也有可能是開啟瞬間電流密度太大,導致大量電子在PN結附近被耗盡區電場加速撞擊。

MOSFET擊穿電壓原因和防護措施

1、MOS管為什么會被靜電擊穿 2、靜電擊穿是指擊穿MOS管G極的那層絕緣層嗎 3、擊穿就一定短路了嗎 4、JFET管靜電擊穿又是怎么回事。

MOS管一個ESD敏感器件,它本身的輸入電阻很高,而柵-源極間電容又非常小,所以極易受外界電磁場或靜電的感應而帶電(少量電荷就可能在極間電容上形成相當高的電壓(想想U=Q/C)將管子損壞),又因在靜電較強的場合難于泄放電荷,容易引起靜電擊穿。靜電擊穿有兩種方式:一是電壓型,即柵極的薄氧化層發生擊穿,形成針孔,使柵極和源極間短路,或者使柵極和漏極間短路;二是功率型,即金屬化薄膜鋁條被熔斷,造成柵極開路或者是源極開路。JFET管和MOS管一樣,有很高的輸入電阻,只是MOS管的輸入電阻更高。

靜電放電形成的是短時大電流,放電脈沖的時間常數遠小于器件散熱的時間常數。因此,當靜電放電電流通過面積很小的pn結或肖特基結時,將產生很大的瞬間功率密度,形成局部過熱,有可能使局部結溫達到甚至超過材料的本征溫度(如硅的熔點1415℃),使結區局部或多處熔化導致pn結短路,器件徹底失效。這種失效的發生與否,主要取決于器件內部區域的功率密度,功率密度越小,說明器件越不易受到損傷。

反偏pn結比正偏pn結更容易發生熱致失效,在反偏條件下使結損壞所需要的能量只有正偏條件下的十分之一左右。這是因為反偏時,大部分功率消耗在結區中心,而正偏時,則多消耗在結區外的體電阻上。對于雙極器件,通常發射結的面積比其它結的面積都小,而且結面也比其它結更靠近表面,所以常常觀察到的是發射結的退化。此外,擊穿電壓高于100V或漏電流小于1nA的pn結(如JFET的柵結),比類似尺寸的常規pn結對靜電放電更加敏感。

所有的東西是相對的,不是絕對的,MOS管只是相對其它的器件要敏感些,ESD有一個很大的特點就是隨機性,并不是沒有碰到MOS管都能夠把它擊穿。另外,就算是產生ESD,也不一定會把管子擊穿。|

靜電的基本物理特征為:

(1)有吸引或排斥的力量;

(2)有電場存在,與大地有電位差;

(3)會產生放電電流。

這三種情形即ESD一般會對電子元件造成以下三種情形的影響:

(1)元件吸附灰塵,改變線路間的阻抗,影響元件的功能和壽命;

(2)因電場或電流破壞元件絕緣層和導體,使元件不能工作(完全破壞);

(3)因瞬間的電場軟擊穿或電流產生過熱,使元件受傷,雖然仍能工作,但是壽命受損。所以ESD對MOS管的損壞可能是一,三兩種情況,并不一定每次都是第二種情況。

上述這三種情況中,如果元件完全破壞,必能在生產及品質測試中被察覺而排除,影響較少。如果元件輕微受損,在正常測試中不易被發現,在這種情形下,常會因經過多次加工,甚至已在使用時,才被發現破壞,不但檢查不易,而且損失亦難以預測。靜電對電子元件產生的危害不亞于嚴重火災和爆炸事故的損失。

電子元件及產品在什么情況下會遭受靜電破壞可以這么說:電子產品從生產到使用的全過程都遭受靜電破壞的威脅。從器件制造到插件裝焊、整機裝聯、包裝運輸直至產品應用,都在靜電的威脅之下。在整個電子產品生產過程中,每一個階段中的每一個小步驟,靜電敏感元件都可能遭受靜電的影響或受到破壞,而實際上最主要而又容易疏忽的一點卻是在元件的傳送與運輸的過程。在這個過程中,運輸因移動容易暴露在外界電場(如經過高壓設備附近、工人移動頻繁、車輛迅速移動等)產生靜電而受到破壞,所以傳送與運輸過程需要特別注意,以減少損失,避免無所謂的糾紛。防護的話加齊納穩壓管保護。

現在的mos管沒有那么容易被擊穿,尤其是是大功率的vmos,主要是不少都有二極管保護。vmos柵極電容大,感應不出高壓。與干燥的北方不同,南方潮濕不易產生靜電。還有就是現在大多數CMOS器件內部已經增加了IO口保護。但用手直接接觸CMOS器件管腳不是好習慣。至少使管腳可焊性變差。

MOSFET擊穿電壓-MOS管被擊穿的解決方案

第一、MOS管本身的輸入電阻很高,而柵源極間電容又非常小,所以極易受外界電磁場或靜電的感應而帶電,而少量電荷就可在極間電容上形成相當高的電壓(U=Q/C),將管子損壞。雖然MOS輸入端有抗靜電的保護措施,但仍需小心對待,在存儲和運輸中最好用金屬容器或者導電材料包裝,不要放在易產生靜電高壓的化工材料或化纖織物中。組裝、調試時,工具、儀表、工作臺等均應良好接地。要防止操作人員的靜電干擾造成的損壞,如不宜穿尼龍、化纖衣服,手或工具在接觸集成塊前最好先接一下地。對器件引線矯直彎曲或人工焊接時,使用的設備必須良好接地。

第二、MOS電路輸入端的保護二極管,其導通時電流容限一般為1mA,在可能出現過大瞬態輸入電流(超過10mA)時,應串接輸入保護電阻。因此應用時可選擇一個內部有保護電阻的MOS管應。還有由于保護電路吸收的瞬間能量有限,太大的瞬間信號和過高的靜電電壓將使保護電路失去作用。所以焊接時電烙鐵必須可靠接地,以防漏電擊穿器件輸入端,一般使用時,可斷電后利用電烙鐵的余熱進行焊接,并先焊其接地管腳。

MOS是電壓驅動元件,對電壓很敏感,懸空的G很容易接受外部干擾使MOS導通,外部干擾信號對G-S結電容充電,這個微小的電荷可以儲存很長時間。在試驗中G懸空很危險,很多就因為這樣爆管,G接個下拉電阻對地,旁路干擾信號就不會直通了,一般可以10~20K。這個電阻稱為柵極電阻

作用1:為場效應管提供偏置電壓;

作用2:起到瀉放電阻的作用(保護柵極G~源極S)。第一個作用好理解,這里解釋一下第二個作用的原理:保護柵極G~源極S:場效應管的G-S極間的電阻值是很大的,這樣只要有少量的靜電就能使他的G-S極間的等效電容兩端產生很高的電壓,如果不及時把這些少量的靜電瀉放掉,他兩端的高壓就有可能使場效應管產生誤動作,甚至有可能擊穿其G-S極;這時柵極與源極之間加的電阻就能把上述的靜電瀉放掉,從而起到了保護場效應管的作用。MOSFET擊穿電壓

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹