影響MOSFET性能有哪些因素?

在追求不斷提高能效的過程中,MOSFET的芯片和封裝也在不斷改進。除了器件結構和加工工藝,MOSFET的性能還受其他幾個周圍相關因素的影響。影響MOSFET性能,這些因素包括封裝阻抗、印刷電路板(PCB)布局、互連線寄生效應和開關速度。事實上,真正的開關速度取決于其他幾個因素,例如切換的速度和保持柵極控制的能力,同時抑制柵極驅動回路電感帶來的影響。

同樣,低柵極閾值還會加重Ldi/dt問題。正因為了解電路中晶體管的性能很重要,所以我們將選用半橋拓撲。這種拓撲是電力電子裝置最常用的拓撲之一。這些例子重點介紹了同步壓降轉換器——一個半橋拓撲的具體應用。

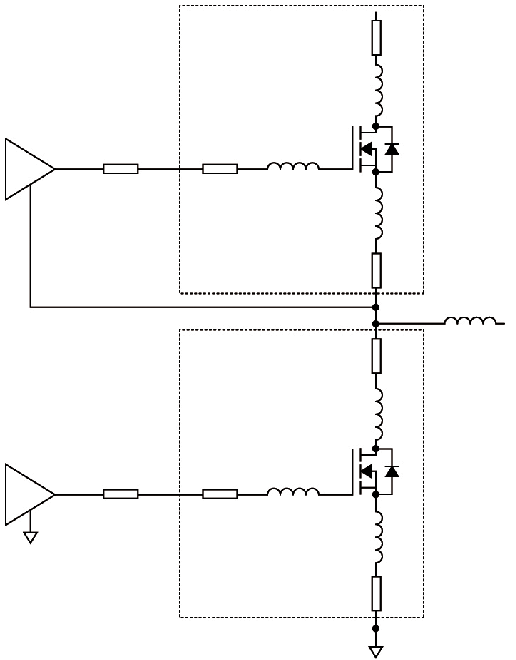

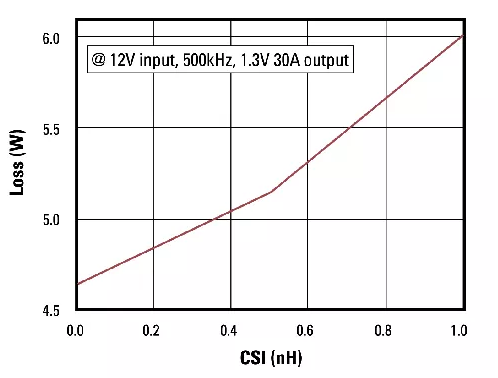

圖1為具備雜散電感和電阻(由封裝鍵合線、引線框以及電路板布局和互連線帶來)等寄生效應的半橋電路。共源電感(CSI)傾向于降低控制FET(高邊FET)的導通和關斷速度。如果與柵極驅動串聯,通過CSI的電壓加至柵極驅動上,可使FET處于導通狀態(條件:V = -Ldi/dt),從而延遲晶體管的關斷。這也會增大控制FET的功耗,如圖2所示。

更高的功耗會導致轉換效率降低。另外,由于雜散電感,電路出現尖峰電壓的可能性很高。如果這些尖峰電壓超過器件的額定值,可能會引起故障。為了消除或使這種寄生電感最小化,設計人員必須采用類似無引腳或接線柱的DirecFET等封裝形式,并采用使互連線阻抗最小化的布局。與標準封裝不同,DirecFET無鍵合線或引線框。

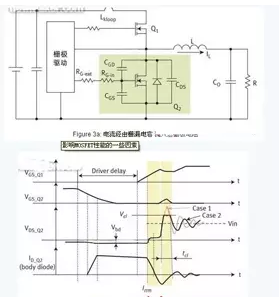

因此,它可極大地降低導通電阻,同時大幅降低開關節點的振鈴,抑制開關損耗。緩和C dv/dt感應導通影響性能的另一個因素是C dv/dt感應導通(和由此產生的擊穿)。C dv/dt通過柵漏電容CGD的反饋作用(引起不必要的低邊FET導通),使低邊(或同步)FET出現柵極尖峰電壓。實際上,當Q2的漏源極的電壓升高時,電流就會經由柵漏電容CGD 流入總柵極電阻RG ,如圖3(a)所示。

因此,它會導致同步FET Q2的柵極出現尖峰電壓。當該柵極電壓超出規定的閾值時,它就會被迫導通。圖3(b)顯示的,正是在圖3(a)所示 典型同步壓降轉換器拓撲中,同步FET Q2在這種工作模式下的主要波形。

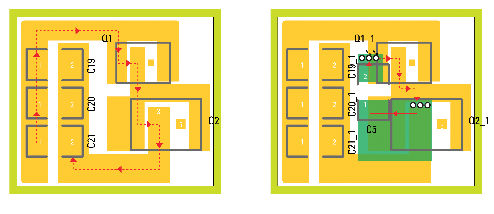

影響MOSFET性能,另一個可影響電源產品設計的MOSFET性能的因素是布局。例如,不合理的電路板布局可增大電源電路的寄生效應,反過來,增大的寄生效應又會提高電源的開關和導通損耗。此外,它還會提高電磁干擾的噪聲水平,從而使設計出的產品達不到理想的性能。若要最大限度降低電路板布局帶來的影響,設計人員必須確保通過將驅動和MOSFET盡可能地背靠背放置,從而使輸入回路面積最小化,如圖4所示。

圖4右側有一個位于FET下方的小型陶瓷支路,利用過孔形成一個極小的輸入回路。因此,需要將支路電容靠近驅動放置,并將輸入陶瓷電容CIN 靠近高邊MOSFET放置。在這里,控制回路FET相對于同步FET具備更高的優先權。如果將FET并聯,需要確保柵極回路阻抗匹配。

另外,該布局必須采用隔離的模擬接地層和功率接地層,使大電流電路形成獨立的回路,從而不干擾敏感的模擬電路。然后,必須將這兩個接地層與PCB布局的一個點連接。此外,設計人員還必須利用多個過孔,使FET與輸入引腳Vin或接地層連接。電路板上任何未用區域必須灌注銅。總之,封裝阻抗、PCB布局、互連線寄生效應和開關速度都是影響電源電路MOSFET性能的重要因素。

因此,要想在高功率密度條件下獲得最佳的轉換效率,必須在設計MOSFET過程中,充分考慮封裝、電路板布局(包括互連線)、阻抗和開關速度。

F3: 實際上,當Q2的漏源極的電壓升高時,電流就會經由柵漏電容CGD 流入總柵極電阻RG ,如圖3(a)所示。因此,它會導致同步FET Q2的柵極出現尖峰電壓。當該柵極電壓超出規定的閾值時,它就會被迫導通。圖3(b)顯示的,正是在圖3(a)所示 典型同步壓降轉換器拓撲中,同步FETQ2在這種工作模式下的主要波形。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹