從器件物理層面看MOSFET的內部結構

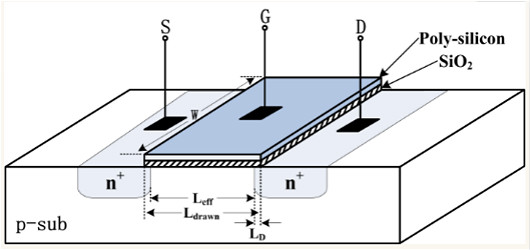

MOSFET的內部結構:MOSFET是Metal-Oxide-Semiconductor Field Effect Transistor的縮寫,即金屬-氧化物-半導體場效應晶體管,是集成電路的基礎。MOSFET都是做在襯底上的,以NMOS為例,如圖,在一塊p型襯底(p-sub,襯底又叫Bulk或Body)上,形成兩塊重摻雜的n+區,分別為源(Source)和漏(Drain);襯底之上用SiO2做一塊絕緣層,叫柵氧化層或柵絕緣層,用Tox表示其厚度,稱為柵絕緣層厚度或柵氧化層厚度;

柵氧化層的上面是柵(grid),若用金屬鋁做柵極則稱為鋁柵,這就是MOSFET名稱中MOS的由來:金屬-氧化物-半導體(Metal-Oxide-Semiconductor)。但是由于多晶硅做柵極的諸多優點,后來用高摻雜的多晶硅(Poly-silicon)代替鋁做柵極,稱作多晶硅柵。

柵在源漏方向的長度稱作柵的長L,垂直方向稱為柵的寬W,需要注意的是,在數量上W比L要大;MOSFET的一個特點是其源和漏是完全對稱的,也就是說源和漏是可以互換的。在MOS中,源定義為提供載流子的端,而漏定義為接收載流子的端。

源和漏也正是依據這一定義來區分:NMOS中導電的載流子是電子,因此接到電路的最低電位以提供電子的是源極;而PMOS中導電的載流子是空穴,因此接到電路最高電位以提供空穴的是源極。當然,一般人們不會這樣說,而是用另一種方式去表達:NMOS的源極要接到電路的最低電位,而PMOS的源極要連接到電路的最高電位。

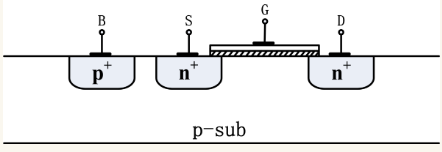

MOSFET的內部結構:圖中的Leff及Ldrawn是到導電溝道的長度,其中Leff稱為有效溝道長度,Ldrawn稱為溝道總長度,并且有如下關系:Leff=Ldrawn-2LD, LD代表橫向擴散長度,是制造工藝中不可避免的誤差。上面的圖中畫出了MOSFET的三個極:源(S)、漏(D)和柵(G),但其實MOSFET是個四端器件,因為還有襯底(B)沒有引出管腳來。下圖中將襯底引出管腳來:

簡單的說,襯底就是一塊做了特定摻雜的硅,但其作用非常重要,并且在電路中襯底的電位對器件的性能有很大影響。MOSFET中的導電溝道也是在襯底中形成:柵極與襯底之間隔有SiO2絕緣層,因此柵與源、漏、襯底之間不導通,而是形成平行板電容器,加電壓時柵與襯底之間形成電場,在該電場的影響下襯底中形成導電溝道,MOS管就開始導通,因此叫場效應晶體管(Field Effect Transistor)。

NMOS中襯底是p型摻雜,工藝上一般用一塊重摻雜的p區作為與外界的接觸,就像上圖中描述的那樣。在電路連接中,一般將MOS的襯底與源連接到一起,使其電位相等。如果襯底的電位與源電位不等,則會存在體效應,引起閾值電壓的偏移。

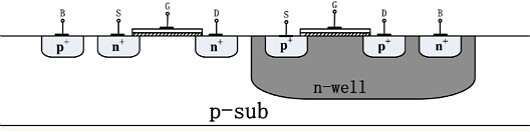

集成電路中大規模應用的CMOS技術,要求在一塊硅片上同時做多個NMOS和PMOS。但是NMOS與PMOS的襯底類型不同,這就要求在工藝上為其中一類晶體管做一個局部襯底,稱為阱,這類晶體管就做在阱中。因此,目前采取的技術是:NMOS直接做在p襯底上,而在需要做PMOS的區域做一塊摻雜的n區,稱為n阱(well),PMOS就做在這個阱中。

因此在CMOS電路中,NMOS共用同一個襯底,而PMOS處在各自的n阱中。這就造成了NMOS和PMOS在襯底處理上的不同:所有NMOS的襯底由于連在一起,處于同一電位,不能保證其襯底與源極的電位完全相同,而各個PMOS的襯底則可以靈活處理。這就是在一般的電路分析中NMOS要考慮體效應而PMOS不用考慮的原因。

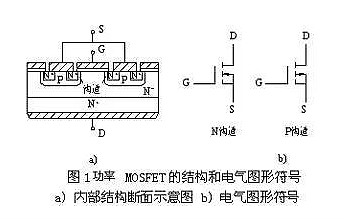

功率MOSFET的內部結構和電氣符號如圖所示;其導通時只有一種極性的載流子(多子)參與導電,是單極型晶體管。導電機理與小功率mos管相同,但 結構上有較大區別,小功率MOS管是橫向導電器件,功率MOSFET大都采用垂直導電結構,又稱為VMOSFET(Vertical MOSFET),大大提高了MOSFET器件的耐壓和耐電流能力。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹