CMOS工藝詳細解析

CMOS工藝與NMOS(或PMOS)工藝不同之處是要在同一個襯底上同時制造出n-溝和p-溝晶體管。在NMOS工藝中看到,襯底的摻雜類型和摻雜水平是按照在它上面要制造的n-溝器件的要求來選擇的。

很明顯,在CMOS工藝中,原材料或者是滿足n-溝器件的要求,或者是滿足p-溝器件的要求,但不能同時滿足兩者的要求。

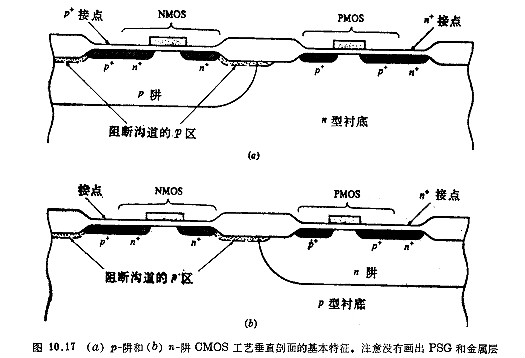

為了適應不能在原材料上制造的那種類型器件的需要,必須形成與原材料摻雜類型相反的區域,如圖10.17中的二個剖面所示。這些摻雜類型相反的區域一般稱為“阱"或“槽”,這里將無區別的使用這兩個詞。

首先要在原材料上將阱區確定出來,然后向阱區注入和擴散摻雜,以得到合適的阱區摻雜濃度和摻雜深度。阱區的摻雜類型成為CMOS工藝的標識特征,例如,圖10.17a中表示了所謂“ p-阱CMOS工藝”,而圖10.17b為“n-阱CMOS工藝”。典型的做法是把P型和n型襯底分別連接到電路中最負的和最正的電壓上,以保證電路工作時p-n結不會正偏。

兩個襯底都要與圖10.17中標志為接點的重摻雜區相接觸,從而得到良好的歐姆接觸。在阱區中,接點更是必不可少的,因為阱區與硅片的其余部分完全是(結)隔離的,而非阱區的襯底很容易從硅片的背面連接引線。要完成圖10.17所示的n-阱和p-阱工藝,它與上節描述的NMOS工藝不同之處主要有三個方面。

首先,在確定壕溝區以前,阱區就要用光刻確定下來,再經注入和擴散。其次,在n型區,要勾劃出(用光刻膠)阻斷溝道的p型注入。事實上,在某些情況下,對主要襯底和阱區分別進行阻斷溝道的注入。

第三,都要形成n﹢型區和p﹢型區,這意味著在注入反型雜質時,這些區域中的每一個必須保護起來(用光刻膠),因此,相對NMOS工藝來說,CMOS工藝要求至少三塊,有時更多附加的掩膜版。值得指出的是CMOS中多晶硅層一般是摻n﹢雜質,即使在PMOS溝道上也是如此,這是因為多晶硅最初的n﹢摻雜很重,當要阻斷p型溝道(即PMOS器件的自對準)而接受p﹢摻雜時,p﹢雜質還不足以補償最初摻入的n﹢雜質,這個問題還要進一步討論。

NMOS和OMOS工藝之間的另-個主要區別是器件間距方面的考慮。NMOS中,相鄰壕溝區之間的最小間距大部分由上節討論的L0C0S技術的結構情況決定,在CMOS中,同種類型器件之間同樣可使用。

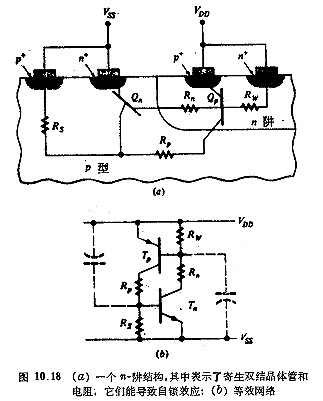

但是,對相反類型器件之間的間距問題的考慮,如p﹢和n﹢間的聞距,就很不相同了。這是由于CMOS具有一種與寄生的導電機制有關的固有的致命弱點,稱作自鎖效應。自鎖效應是一種閘流管的工作機制,很容易觸發。

當然,在CMOS中,在一個芯片上提供了許多這種類型的結構,如果任何一個被觸發到進入自鎖狀態,則就會有很大的電流流動,從而經常使整個片子造成不可恢復的毀壞。圖10.18a表示了典型的n-阱CMOS結構的剖面圖,并集中注意它自鎖的可能性。p型襯底的n﹢區和n型襯底的p﹢區各自分別為NMOS和PMOS晶體管的一部分。

要防止自鎖效應,晶體管的β值一定要小,電阻值一定要小,特別是Rw和Rs的值。對給定的工藝來說,這些條件意味著一些特定的最小間距:

1.n﹢和p﹢間距要足夠遠以防止橫向npn晶體管的βn過高(確保它的基區很長)。

2.阱區要在幾個互相十分靠近的地方通過n﹢接點連接起來,從而使Rw保持很小。

例如對迄今所討論的簡單CMOS工藝來說,n﹢到p﹢的最小間距例如為15μm或更大些,這與n﹢到n﹢和p﹢到p﹢的間距為5μm或更小些相比較,可能是很大的了。為著手解決n﹢到p﹢的間距和自鎖敏感這個關鍵性問題,提出了幾種新的CMOS工藝。

這些工藝的關鍵的一點是在重摻雜的硅片上生長的外延層作為襯底,并在外延層上制造阱區和器件。例如,在一個n-阱CMOS工藝中,最后阱深為5μm,那么使用的原材料是由p型重摻雜的硅片帶有一層厚約10μm的P型輕摻雜的外延層(或“epi”)構成的,外延層均勻摻雜水平選擇到適合于制造NMOS晶體管。

一般,外延層厚度大約二倍于阱深,因為阱區雜質向體內擴散時,外延層下面的重摻雜襯底中的雜質將會向表面擴散。這道工序要設計得使阱區底部最后十分靠近重摻雜的襯底區,因為體內重摻雜區與表面非常接近時,橫向雙結晶體管(上面的例子為npn)的增益和Rg(和Rp)的值兩者都急劇地減小。

作為一級近似 ;在外延-CMOS工藝中,n﹢和p﹢間的最小間距可以減小到約為輕摻雜的外延層的厚度,如上面討論的,這一厚度近似與阱深相同。另一個以外延為基底的CMOS工藝是所謂“雙阱”或“雙槽”工藝。它與早先敘述的其它外延工藝不同之處是外延層摻雜到比制造p-溝或n-溝MOSFET所要求的還要低得多的水平。

對n-溝和p-溝MOSFET的襯底區域都單獨的注入和擴散,而不是只對一種類型的阱區進行注入和擴散,這是該工藝名稱的來由。雙阱工藝與常用的單阱工藝相比的優點在于它去除了單阱摻雜水平常常必須比外延層摻雜要高的這一限制,兩個襯底摻雜都各自按器件類型的要求進行優化。

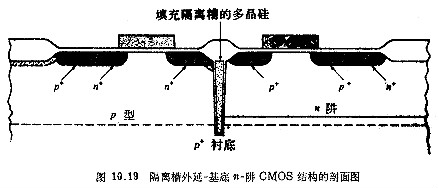

依據n﹢和p﹢間最小間距,相對于非外延工藝來說,所有基于外延襯底的CMOS工藝都有相似的優點。當進一步減小這間距時,要求有更積極的阱區隔離技術,其中許多技術目前還在研究中。其中最有生命力的是所謂“隔離槽”技術。

由圖10.19可以看到這項技術包括沿著阱區周圍嚴格挖一個深槽,并使之進入重摻雜襯底區域。然后用CVD淀積薄膜的技術把隔離槽重新填充使得硅表面幾乎成為平面。通常這薄膜是多晶硅,在槽壁和底部生長一層SiO薄膜之后,在槽中淀積多晶硅以填槽保形。隔離槽的作用是抑制橫向雙結晶體管的電流增益,所以,這一工藝可以避免自鎖效應。

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹