自從1947年第一支晶體管的發(fā)明,半導(dǎo)體集成電路在二十世紀(jì)的后三十年有了一個(gè)極大的發(fā)展。這個(gè)發(fā)展極大的推動(dòng)了世界性的產(chǎn)業(yè)革命和人類社會(huì)的進(jìn)步。 今天在我們每個(gè)人的日常生活中, 英特網(wǎng),手機(jī)的普及和計(jì)算機(jī)在各個(gè)領(lǐng)域的大量應(yīng)用,已經(jīng)使我們進(jìn)入了信息時(shí)代。在這中間起決定性作用的是在硅晶片上工作的CMOS場(chǎng)效應(yīng)晶體管的發(fā)明,它的制造工藝的不斷發(fā)展和以它為基礎(chǔ)的超大規(guī)模集成電路的設(shè)計(jì)手段的不斷改進(jìn)。

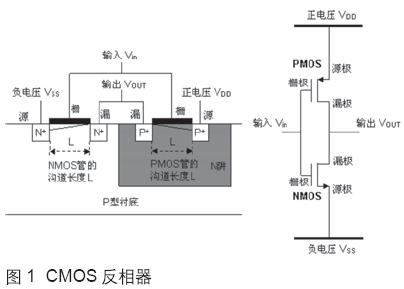

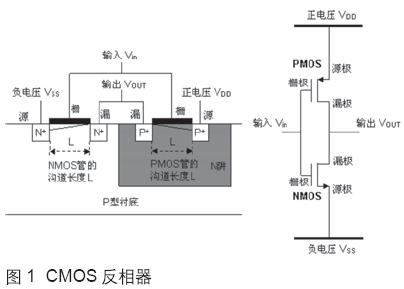

圖1是一個(gè)最基本的CMOS邏輯門—反向器的物理結(jié)構(gòu)和電路圖。當(dāng)輸入為邏輯0時(shí)它的輸出為邏輯1,當(dāng)輸入為邏輯1時(shí)它的輸出為邏輯0。它是構(gòu)成超大規(guī)模集成電路的一個(gè)最基本的元件之一。在這個(gè)電路里有兩個(gè)我們必須要考慮的最重要的參數(shù)。

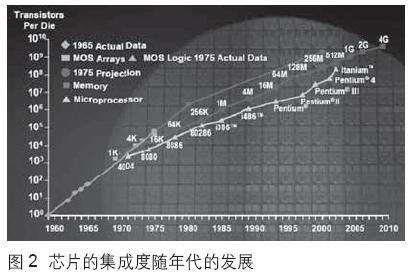

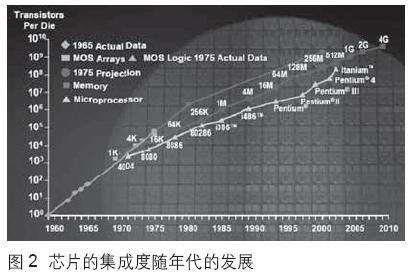

一個(gè)是它的功耗PD,另一個(gè)是場(chǎng)效應(yīng)管的溝道長(zhǎng)度L。 對(duì)于第一個(gè)參數(shù)我們必須要讓它的值最小,這樣我們才可以在一個(gè)很小的硅晶片上集成上幾百萬(wàn)個(gè)晶體管而不讓它發(fā)熱。CMOS數(shù)字集成電路相對(duì)于其它工藝的集成電路是它的功耗非常低。例如上面的反相器它的靜態(tài)功耗幾乎為零而它的動(dòng)態(tài)功耗在納瓦(nW)甚至在皮瓦(pW)級(jí)。因此現(xiàn)代集成電路幾乎全部是用CMOS工藝。 關(guān)于第二個(gè)參數(shù),是場(chǎng)效應(yīng)管的溝道長(zhǎng)度L。 我們也需要讓它的值盡可能的小。這樣器件的工作速度或頻率就很高,因?yàn)闇系篱L(zhǎng)度變小,管子的體積也隨之減小,整個(gè)電路的集成度就高。根據(jù)CMOS 管的按比例縮小原理 [1],在一階近似的情況下當(dāng)管子的溝道長(zhǎng)度和寬度同時(shí)變小a倍,在器件內(nèi)建電場(chǎng)不變得情況下,它的工作電壓將減小a倍,功耗將減小a2倍,而集成度將增加a2倍。同時(shí)管子的工作速度也增加a倍。由于這些原因,在全世界范圍內(nèi),從CMOS場(chǎng)效應(yīng)管工藝發(fā)明之日起,各大半導(dǎo)體制造公司都把減小場(chǎng)效應(yīng)管的溝道長(zhǎng)度作為研究與開發(fā)的最主要的重點(diǎn)。1965年美國(guó)的英特爾公司(Intel)的創(chuàng)始人G. MOORE總結(jié)了集成度隨年份增長(zhǎng)的數(shù)據(jù),得出平均每一年在每一芯片上集成的平均晶體管數(shù)目將增加一倍的結(jié)論,稱為 摩爾定律[2]。由于考慮到管子的數(shù)目增加,系統(tǒng)的功能也越來(lái)越復(fù)雜,G. MOORE本人在1975年修改了這條定律,把它從每一年改為每?jī)赡辍5珡陌雽?dǎo)體產(chǎn)業(yè)的發(fā)展情況看,實(shí)際結(jié)果是每十八個(gè)月。圖2 是由英特爾公司提供的資料[3]。我們可以看到正是由于管子溝道長(zhǎng)度的減小,集成度的提高,才使得半導(dǎo)體存儲(chǔ)器和微處理機(jī)發(fā)展到今天這個(gè)水平。

但是,任何事物的發(fā)展都有兩面性。由于CMOS場(chǎng)效應(yīng)管溝道長(zhǎng)度的減小,當(dāng)它的值小到一定的時(shí)候,將被一些器件的物理參數(shù)和制造工藝的極限所限制。在這篇文章中,我們將討論這些物理參數(shù)和制造工藝的極限并給出CMOS集成電路在21世紀(jì)前二十年的發(fā)展趨勢(shì)。

CMOS場(chǎng)效應(yīng)管的物理參數(shù)極限

·最小允許的場(chǎng)效應(yīng)溝通道長(zhǎng)度

我們知道MOS場(chǎng)效應(yīng)管的一個(gè)最基本的功能是一個(gè)可控開關(guān)。在圖3 中我們可以看到:當(dāng)NMOS管的柵源電壓VGS大于管子的閾值電壓Vth時(shí),MOS管導(dǎo)通就像一根導(dǎo)線一樣。而當(dāng)柵源電壓VGS小于管子的閾值電壓Vth時(shí),MOS將進(jìn)入截止區(qū)域,漏源電流IDS為零就像一個(gè)開路一樣。

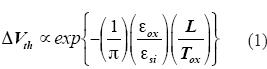

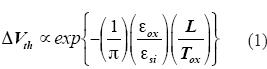

最小溝道長(zhǎng)度對(duì)于一個(gè)CMOS場(chǎng)效應(yīng)管來(lái)說(shuō)是最關(guān)鍵的限制[4]。根據(jù)場(chǎng)效應(yīng)管的微電子學(xué)原理,當(dāng)溝道長(zhǎng)度減小時(shí),橫跨場(chǎng)效應(yīng)管漏極和源極區(qū)域的電場(chǎng), 有時(shí)我們也稱單向橫場(chǎng),將增加。作為一個(gè)結(jié)果,場(chǎng)效應(yīng)管柵極控制管子溝道導(dǎo)通的能力將下降。這就是我們所說(shuō)的場(chǎng)效應(yīng)管的短?hào)判?yīng)[5]。而且這個(gè)效應(yīng)隨著漏極到源極電壓的增加也變得越來(lái)越嚴(yán)重,直接導(dǎo)致場(chǎng)效應(yīng)管的閾值電壓Vth 的減小,亞閾值泄漏電流的增加。在這種情況下,場(chǎng)效應(yīng)管將不能以我們所期望的理想的可控開關(guān)的形式來(lái)工作。根據(jù)MOS管的微電子學(xué)原理, 在一階近似的情況下,MOS 管的閾值電壓的變化DVth與管子的溝道長(zhǎng)度L的自然指數(shù)成正比關(guān)系。 我們有[4]:

其中eox和esi分別是柵極氧化層和管子硅溝道的介電常數(shù),Tox是柵極氧化層的厚度。從這個(gè)關(guān)系中我們看到,當(dāng)管子的溝道長(zhǎng)度L減小到與管子的柵極氧化層的厚度Tox在同一個(gè)數(shù)量級(jí),管子的閾值電壓將急劇的減小。 這就構(gòu)成了最小允許的場(chǎng)效應(yīng)管溝道長(zhǎng)度。

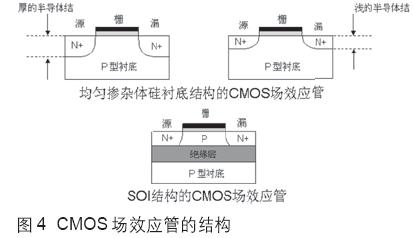

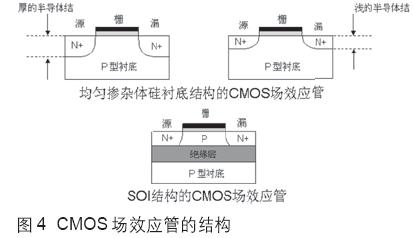

為了減小MOS 管的短?hào)判?yīng),主要的科研工作是改進(jìn)柵極對(duì)整個(gè)管子溝道的控制能力[4]。從這方面入手,在近二十年來(lái),人們從薄的源極漏極擴(kuò)散結(jié)到不同型式的溝道摻雜注入結(jié)構(gòu),從經(jīng)典的體硅襯底到SOI(Silicon On Insulator), 大量的MOS場(chǎng)效應(yīng)管結(jié)構(gòu)已經(jīng)被研究。圖4給出了一些最重要的研究結(jié)果。今天人們從模擬的結(jié)果預(yù)測(cè)10至15納米的溝道長(zhǎng)度將是MOS管按比例縮小的物理極限[6]。更進(jìn)一步,當(dāng)管子的溝道長(zhǎng)度小于這個(gè)尺寸,量子隧道效應(yīng)將顯著增加以導(dǎo)致MOS管的柵極將完全損失掉對(duì)溝道的控制能力,這樣MOS管將不能完全截止導(dǎo)致它將不能完成最基本的開關(guān)功能。

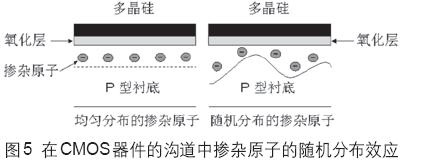

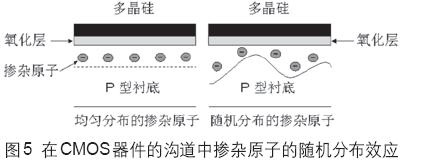

·溝通道摻雜源自排列的隨機(jī)效應(yīng)

根據(jù)MOS管的微電子學(xué)原理,在用離子注入時(shí),摻雜原子在器件溝道位置的隨機(jī)變化將影響MOS管電參數(shù)的變化。當(dāng)MOS管的尺寸減小時(shí),摻雜原子在器件中的平均數(shù)量將減小。作為一個(gè)結(jié)果,摻雜原子數(shù)目和它們?cè)谄骷系乐械乃谖恢玫碾S機(jī)變化將增加[7]。圖5 將說(shuō)明這種情況。在標(biāo)準(zhǔn)的制造工藝中,摻雜原子通過(guò)隨機(jī)散射過(guò)程在溝道中找到它們的所在位置。因此,摻雜原子在溝道中的數(shù)目和排列的隨機(jī)效應(yīng)是器件的固有效應(yīng),人們不能在標(biāo)準(zhǔn)的制造工藝中把它們?nèi)∠簟_@個(gè)效應(yīng)將導(dǎo)致器件和整個(gè)電路的性能, 例如電流的驅(qū)動(dòng)能力和傳輸滯后的隨機(jī)變化。其中摻雜原子在溝道中的數(shù)目和排列的隨機(jī)效應(yīng)也將引起MOS管閾值電壓的隨機(jī)變化。這些將直接導(dǎo)致由于溝道長(zhǎng)度減小而使器件的性能變壞。

·耗盡層的厚度和半導(dǎo)體界的厚度

一般來(lái)說(shuō),為了減小MOS管的短溝 道效應(yīng), 器件的耗盡層的厚度和源極與漏極的半導(dǎo)體結(jié)的厚度要盡可能的薄。而器件的耗盡層的厚度和源極與漏極半導(dǎo)體結(jié)的厚度的形成是通過(guò)離子注入的方式控制要被注入的摻雜原子到被選中的區(qū)域和限制它們的熱運(yùn)動(dòng)。當(dāng)器件的尺寸減小時(shí),理論計(jì)算要求現(xiàn)代MOS 管有一個(gè)較為陡峭的摻雜剖面[8]。在MOS管的制造過(guò)程中,這個(gè)陡峭的摻雜剖面要求對(duì)于控制耗盡層厚度和源極與漏極半導(dǎo)體結(jié)厚度的形成是一個(gè)極大的挑戰(zhàn)。在這方面,SOI MOS場(chǎng)效應(yīng)管結(jié)構(gòu)是一個(gè)最好的選擇。但是這種結(jié)構(gòu)也有它的局限性,例如:高電場(chǎng)下的導(dǎo)電子的遷移率的減小和量子化閾值電壓的變化[8]。

·最小柵極氧化層厚度

為了保證MOS管的短溝道效應(yīng)在可控制的范圍內(nèi)和保持一個(gè)好亞閾值截止特性,正像關(guān)系式(1)所指出的那樣,柵極氧化層厚度Tox需要減小到與場(chǎng)效應(yīng)管的溝道長(zhǎng)度L來(lái)比差很多倍[9]。例如:對(duì)于一個(gè)100納米溝道長(zhǎng)度的MOS管,在1.5 伏的工作電壓下,它的柵極氧化層厚度應(yīng)該是在3納米的范圍。這個(gè)3納米的厚度大約相當(dāng)于十個(gè)硅原子緊密排列的厚度[7]。對(duì)于這樣一個(gè)氧化層厚度,量子力學(xué)的遂道效應(yīng)將發(fā)生。這直接導(dǎo)致柵極的泄漏電流隨氧化層厚度的減小而成指數(shù)型的增加。對(duì)于經(jīng)典的體硅襯底MOS管,柵極的泄漏電流的增加將引起整個(gè)電路的靜態(tài)功耗的增加,而相對(duì)于SOI MOS管結(jié)構(gòu),柵極泄漏電流將顯著的引起管子溝道的電位變化,從而影響器件的閾值電壓和整個(gè)電路的功能。柵極氧化層厚度減小的另一個(gè)效應(yīng)是MOS管子反型層導(dǎo)電子的丟失和器件跨導(dǎo)的減小[8]。這主要是由于氧化層厚度減小,導(dǎo)致管子反型層的量子化和多晶硅柵極的耗盡。這些都降低了柵極對(duì)器件溝道的控制能力。因此柵極氧化層的遂道電流和管子反型層導(dǎo)電子的丟失是柵極氧化層厚度減小的最主要的限制。它們也直接限制了CMOS場(chǎng)效應(yīng)管尺寸的進(jìn)一步減小[9]。為了減小這些效應(yīng),人們可以采用高介電常數(shù)的柵極氧化層和用金屬柵極來(lái)替代經(jīng)典的多晶硅柵極等辦法來(lái)解決。

·最小供電電壓

根據(jù)MOS場(chǎng)效應(yīng)管的按比例縮小原理,在保持溝道電場(chǎng)為常數(shù)的情況下,電路的供電電壓也將按比例縮小。然而,為了維持與最近十年來(lái)所開發(fā)的系統(tǒng)的兼容性(它們經(jīng)常需要5 伏的供電電壓),半導(dǎo)體制造商已不太愿意進(jìn)一步的減小電路的工作電壓以使得整個(gè)電路的功耗與可靠性變得不可控制[6]。在通常,整個(gè)電路的功耗Pchip是電路工作功耗Pactive與截止功耗Poff的總和[9]:

CSW是電路結(jié)點(diǎn)的總電容,VDD是工作電壓,f是開關(guān)的時(shí)鐘頻率,Wtotal是所有截止器件的寬度,Ioff是每個(gè)器件的截止電流。從(2)至(4)式所指出的那樣,減小工作電壓是減小功耗的最有效的方法。但減小供電電壓不光只是減小了系統(tǒng)功耗同時(shí)也削弱了系統(tǒng)工作的可靠性,特別是在器件按比例縮小以提高系統(tǒng)的集成度和工作速度的情況下。

非常不幸,存在一個(gè)最小的工作電壓。這是由于為了保持器件有較高的工作速度,它的閾值電壓Vth應(yīng)該與供電電壓VDD成正比的減小。然而當(dāng)管子閾值電壓減小時(shí),它的截止電流隨這個(gè)電壓值的減小而成指數(shù)型增加。由于電流的增加而MOS管的截止功耗也增加。在現(xiàn)代大多數(shù)集成電路的設(shè)計(jì)中,整個(gè)電路系統(tǒng)可采納的截止功耗要求最小閾值電壓Vth是在300毫伏左右,這就要求最小供電電壓在1伏左右[6]。這顯然與大多數(shù)已開發(fā)的系統(tǒng)不兼容,需要重新來(lái)實(shí)現(xiàn),直接導(dǎo)致工作量的大量增加。

·器件連線的分布電阻與分布電容

與器件的按比例縮小原理相反,器件連線的分布電阻和分布電容隨連線寬度的減小而增加。因此,這也從電路的工作速度和集成度方面對(duì)按比例縮小的CMOS工藝構(gòu)成一個(gè)限制。為了克服連線分布電阻的問(wèn)題,在幾年前,銅連線的工藝被引進(jìn)。而對(duì)于分布電容人們也研究了很多低介電常數(shù)的連線與硅基片的絕緣層接構(gòu)。今天,由于器件連線分布電阻電容在不同器件之間所引起的時(shí)間滯后效應(yīng)一直是現(xiàn)代CMOS工藝發(fā)展的主要限制之一。如果可能,一個(gè)有潛力的發(fā)展是用超導(dǎo)連線。

·新的CMOS場(chǎng)效應(yīng)管的發(fā)展方向

為了更進(jìn)一步的減小CMOS管的尺寸,人們已經(jīng)從理論上研究了很多器件結(jié)構(gòu)。而單晶硅被集成在絕緣體上的結(jié)構(gòu)(SOI)是最有發(fā)展前途的而且被許多像IBM,MOTOROLA和AMD等大的半導(dǎo)體制造公司所采納。相對(duì)于經(jīng)典的體硅CMOS 結(jié)構(gòu),SOI CMOS結(jié)構(gòu)的最大不同是像在圖3 所描數(shù)的那樣,人們?cè)诠杈屑恿艘粋€(gè)氧化埋層,也就是一個(gè)絕緣層。用這種結(jié)構(gòu)所制造的微處理機(jī)比用體硅晶體所制造的同樣的微處理機(jī)要快20~35%[6]。同時(shí)在低功率應(yīng)用中,由于SOI CMOS工藝的小的寄生電容,也使這種工藝被大量的采納。

CMOS場(chǎng)效應(yīng)管的制造工藝極限

·半導(dǎo)體的光刻工藝

這已經(jīng)被證明現(xiàn)代半導(dǎo)體光刻工藝是有這個(gè)能力使人們隨器件按比例縮小而制造超大規(guī)模集成電路(ULSI)。但是,要用今天的光刻工藝來(lái)制造在納米范圍的CMOS場(chǎng)效應(yīng)管是一個(gè)非常重要的待解決問(wèn)題。經(jīng)典的光學(xué)光刻工藝的精確度由于運(yùn)用了改進(jìn)的數(shù)字快門鏡頭和較短波長(zhǎng)的激光源已經(jīng)超過(guò)了理論預(yù)測(cè)的很多倍。現(xiàn)在,最先進(jìn)的用于大規(guī)模制造集成電路的光刻設(shè)備是用波長(zhǎng)為193納米的激光源[9]。一些光刻精確度的改進(jìn)技術(shù),例如可控相位變化技術(shù)等,已使我們有能力讓圖形的精確度在100納米的這個(gè)范圍內(nèi)。這個(gè)技術(shù)運(yùn)用的是光學(xué)的干涉原理到硅晶片上的圖形變化比較大的區(qū)域。因此,它不是幾何圖形獨(dú)立的,可控相位變化技術(shù)不能用于整個(gè)芯片中所有器件的制造。對(duì)于小于100納米的范圍,經(jīng)典的光學(xué)光刻技術(shù)只能用在精度要求不高的地方,而精度要求高的地方,我們必須用X射線光刻或電子束光刻技術(shù)[9]。

對(duì)于小于100納米的CMOS工藝,為了獲得高精度的MOS管的圖形,X射線光刻技術(shù)的應(yīng)用是非常重要的。這個(gè)技術(shù)應(yīng)用的主要問(wèn)題是掩膜版的制造[8]。相對(duì)于X射線光刻技術(shù),在小于100納米的應(yīng)用范圍,另一個(gè)有效的光刻技術(shù)是用極端紫外光 (EUV)。這個(gè)技術(shù)用的是一個(gè)13納米波長(zhǎng)的反射光。

在近幾年的科研領(lǐng)域,納米結(jié)構(gòu)的圖形光刻是用電子束光刻技術(shù)。它的光刻精確度是在10納米的范圍。對(duì)于電子束光刻技術(shù),它的最大挑戰(zhàn)是怎樣把它與一般的光刻技術(shù)結(jié)合起來(lái)來(lái)加以應(yīng)用。

·三維立體集成技術(shù)

相對(duì)于兩維平面集成電路,三位立體集成技術(shù)已被人們提出,它主要有兩點(diǎn)好處:1) 減小了器件之間的連線長(zhǎng)度,2) 由于整個(gè)芯片尺寸的減小而導(dǎo)致可靠性的提高,進(jìn)而降低了芯片的造價(jià)。三維立體集成技術(shù)相對(duì)于將來(lái)的CMOS工藝是非常具有吸引力的,特別是在系統(tǒng)芯片(SoC)的應(yīng)用上。運(yùn)用三維立體集成技術(shù),對(duì)于不同的集成電路,人們能夠先把它們分別制造,然后再把它們連接起來(lái)。三維立體集成技術(shù)的主要困難在于:不同電路層的對(duì)準(zhǔn)與絕緣問(wèn)題;這些不同層的連接技術(shù);還有在絕緣層上重新集成硅晶體和整個(gè)芯片的散熱技術(shù)問(wèn)題。

·低介電常數(shù)的絕緣介質(zhì)和超導(dǎo)傳輸?shù)募夹g(shù)問(wèn)題

對(duì)于不同器件的連接, 人們新進(jìn)的用化學(xué)機(jī)械拋光技術(shù)(CMP )使銅線代 替鋁線。但用銅線代替鋁線,好的方面是降低了連線的分布電阻,壞的方面是連線的可靠性變壞[9]。同時(shí),銅連線將不能非常充分的消除整個(gè)連線的時(shí)間滯后,因?yàn)檫@個(gè)滯后是分布電阻和電容的乘積。為了降低連線分布電容,金屬連線層的低介電常數(shù)絕緣介質(zhì)的研究是非常重要的。在這方面已經(jīng)有許多低介電常數(shù)的絕緣介質(zhì)被研究。為了減小連線電阻,高溫超導(dǎo)是一個(gè)最理想的選擇。但依據(jù)它的研究現(xiàn)狀,在最近的將來(lái)把它應(yīng)用到CMOS場(chǎng)效應(yīng)管工藝還是有很多困難。

MOS場(chǎng)效應(yīng)管新的制造工藝的發(fā)展方向

為了更進(jìn)一步減小CMOS場(chǎng)效應(yīng)管的尺寸以滿足現(xiàn)代信息社會(huì)的要求,人們需要一些新的制造工藝以克服由于器件尺寸減小而帶來(lái)的挑戰(zhàn)。這包括材料科學(xué)的發(fā)展和制造設(shè)備的革新。在CMOS場(chǎng)效應(yīng)管新的制造工藝的發(fā)展方向的挑戰(zhàn)主要集中在以下方面;如何控制工藝的變化;如何改進(jìn)生產(chǎn)率;如何平衡各種工藝的革新和研究與開發(fā)的投資。 總之, 根據(jù)人們的預(yù)測(cè),半導(dǎo)體工業(yè)根據(jù)CMOS場(chǎng)效應(yīng)管按比例縮小原理可以保持它的發(fā)展一直到2020年以達(dá)到管子的最小溝道長(zhǎng)度在10至15納米這個(gè)范圍[10]。

結(jié)語(yǔ)

CMOS場(chǎng)效應(yīng)管的工藝發(fā)展和它的局限由于它在現(xiàn)代信息社會(huì)的重要性是一個(gè)非常廣范的討論題目。它的發(fā)展還像以前一樣繼續(xù)產(chǎn)生許多博士論文以帶來(lái)科學(xué)與工程的變革。在這篇文章里,我們主要是想簡(jiǎn)要的討論當(dāng)CMOS工藝更近一步發(fā)展它的物理參數(shù)和制造工藝的限制。

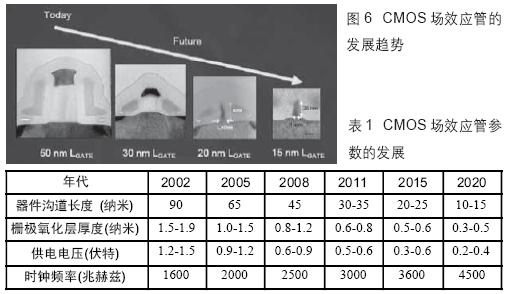

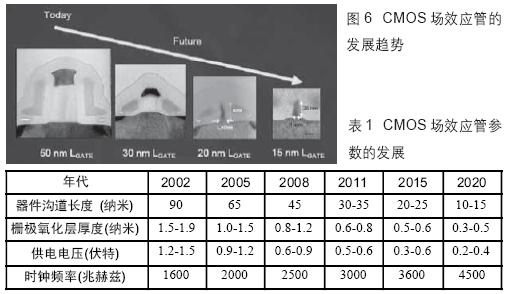

圖6和表1 是英特爾公司在21世紀(jì)前二十年預(yù)測(cè)[3][10]:

我們可以看到,CMOS集成電路工藝還將繼續(xù)按比例縮小一直到10至15納米這個(gè)范圍。為了制造十幾納米長(zhǎng)的器件,許多非常艱巨的挑戰(zhàn)必須被克服。現(xiàn)在人們還不太清楚經(jīng)典的CMOS場(chǎng)效應(yīng)管的溝道長(zhǎng)度是否可以減小到10納米以下。因此, 除非有一個(gè)革命性的重大突破,否則,以CMOS 集成電路為基礎(chǔ)而建立起的半導(dǎo)體工業(yè)將完成它光榮的高增長(zhǎng)歷史使命而變成像鋼鐵工業(yè)和汽車工業(yè)一樣的傳統(tǒng)工業(yè)。

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹