在集成電路中,在通常橫截面為50乘50密耳的小硅晶片上開發了大量的有源和無源元件及其互連。制造這種電路所遵循的基本工藝包括外延生長,掩模雜質擴散,氧化物生長和氧化物蝕刻,使用光刻法制造圖案。

晶圓上的元件包括電阻器,晶體管,二極管,電容器等......制造IC最復雜的元件是晶體管。晶體管有各種類型,如CMOS,BJT,FET。我們根據要求選擇在IC上實現的晶體管技術類型。在本文中,讓我們熟悉CMOS制造(或)制造晶體管作為CMOS管的概念。

CMOS晶體管制造工藝

為了降低功耗要求,CMOS技術用于實現晶體管。如果我們需要更快的電路,則使用 BJT在IC上實現晶體管。作為IC的CMOS晶體管的制造可以用三種不同的方法完成。

N阱/ P阱技術,其中在p型襯底或p型擴散上進行n型擴散,分別在n型襯底上完成。

CMOS晶體管的雙阱技術,其中NMOS和PMOS晶體管,通過同時擴散在外延生長基極發展了晶片,而不是基底上。

硅絕緣體工藝,其中不使用硅作為襯底,而是使用絕緣體材料來提高速度和閂鎖敏感性。

N井/ P井技術

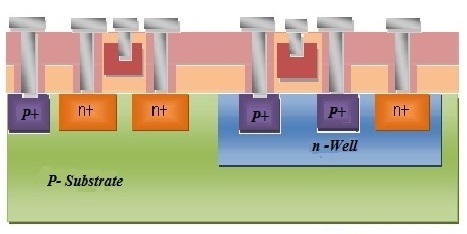

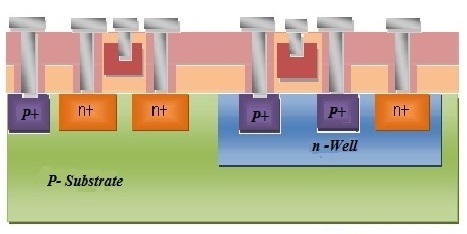

可以通過在同一硅晶片上集成NMOS和PMOS晶體管來獲得CMOS晶體管。在N阱技術中,n型阱擴散在p型襯底上,而在P阱中則是反之亦然。

CMOS晶體管的制造步驟

在CMOS晶體管制造工藝流程是使用20基本的制造步驟進行,同時使用N-阱/ P阱技術制造。

用N阱制作CMOS

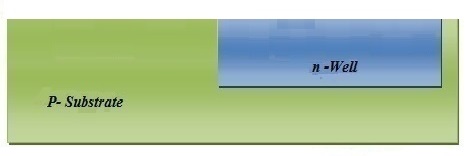

步驟1:首先,我們選擇基板作為制造基礎。對于N阱,選擇P型硅襯底。

基質

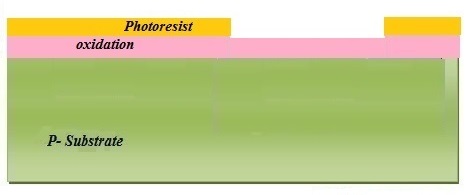

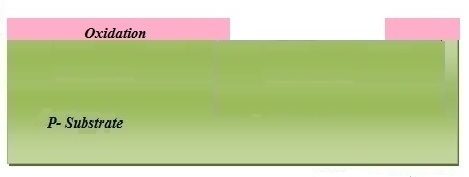

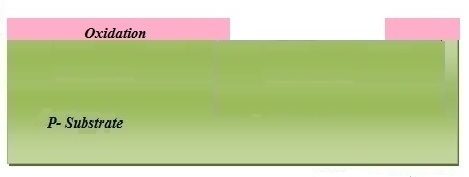

步驟2 - 氧化:使用SiO 2作為阻擋層來實現n型雜質的選擇性擴散,該阻擋層保護晶片的部分免受基板的污染。SiO 2是由氧化工藝布局進行將襯底暴露于高品質的氧和氫在氧化室中在約1000 ℃。

氧化

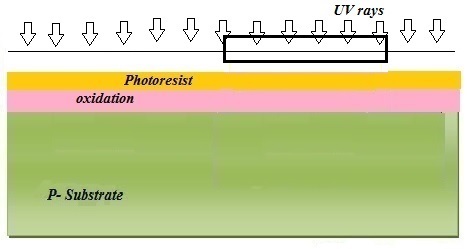

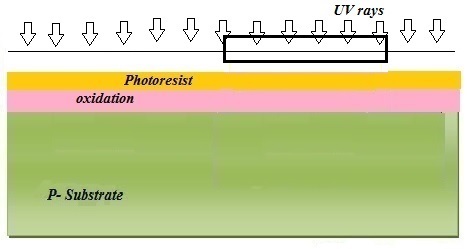

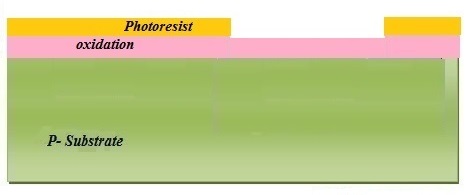

步驟3 - 光致抗蝕劑的生長:在允許選擇性蝕刻的這個階段,對SiO2層進行光刻處理。在該過程中,晶片涂有均勻的光敏乳液膜。

光刻膠的成長

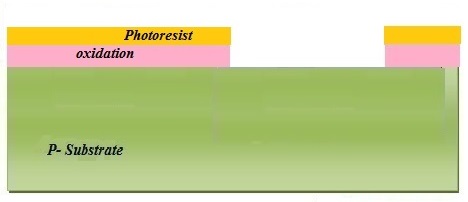

步驟4 - 掩蔽:該步驟是光刻工藝的繼續。在該步驟中,使用模板制作所需的開放圖案。該模版用作光刻膠上的掩模。現在將基板暴露于紫外線,存在于掩模的曝光區域下的光致抗蝕劑聚合。

遮蔽光刻膠

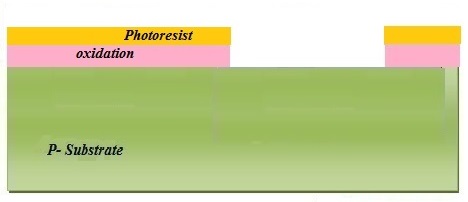

步驟5 - 去除未曝光的光致抗蝕劑:去除掩模,并通過使用諸如三氯乙烯的化學品顯影晶片來溶解光致抗蝕劑的未曝光區域。

去除光刻膠

步驟6 - 蝕刻:將晶片浸入氫氟酸的蝕刻溶液中,從摻雜劑將要擴散的區域除去氧化物。

蝕刻SiO2

步驟7 - 去除整個光致抗蝕劑層:在蝕刻過程中,受光致抗蝕劑層保護的那些SiO2部分不受影響。現在用化學溶劑(熱H2SO4)剝離光刻膠掩模。

去除光刻膠層

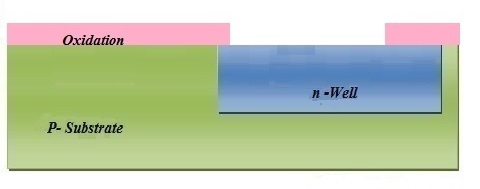

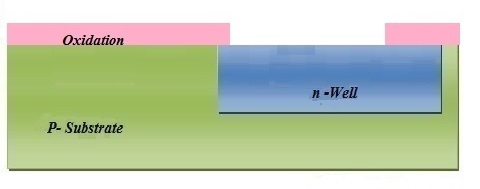

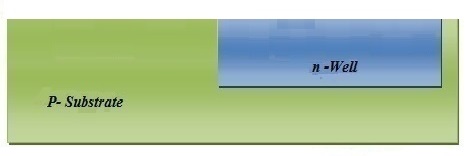

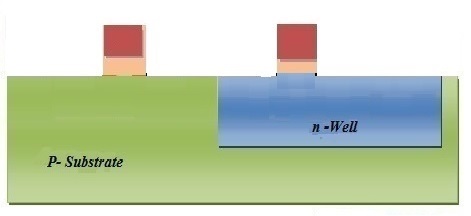

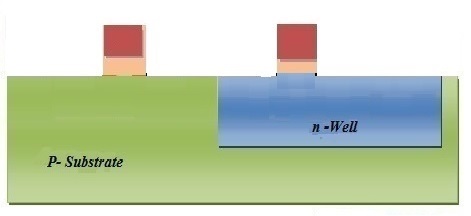

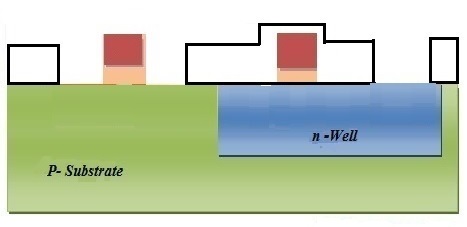

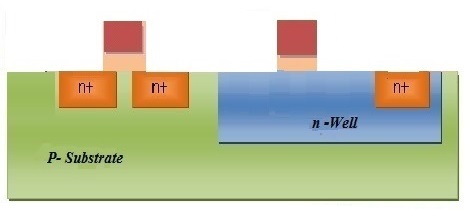

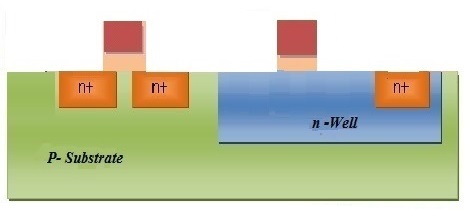

步驟8 - N阱的形成: n型雜質通過暴露區域擴散到p型襯底中,從而形成N阱。

N阱的形成

步驟9 - 去除SiO 2:現在通過使用氫氟酸除去SiO 2層。

去除SiO2

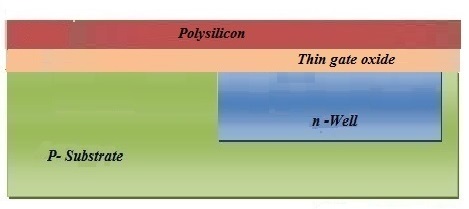

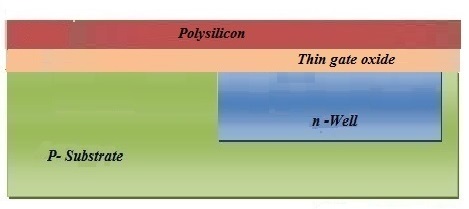

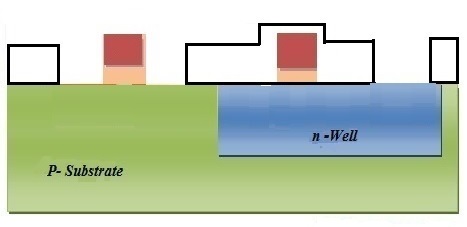

步驟10 - 多晶硅的沉積:CMOS晶體管的柵極的未對準將導致不希望的電容,這可能損害電路。因此,為了防止這種“自對準柵極工藝”是優選的,其中在使用離子注入形成源極和漏極之前形成柵極區域。

多晶硅的沉積

多晶硅被用于形成柵極的,因為它可以承受高溫大于8000 0 c當一個晶片進行退火方法形成源極和漏極的。通過使用化學沉積工藝在薄的柵極氧化物層上沉積多晶硅。多晶硅層下面的這種薄柵極氧化物防止在柵極區域下進一步摻雜。

步驟11 - 柵極區域的形成:除了形成NMOS和PMOS晶體管的柵極所需的兩個區域之外,多晶硅的剩余部分被剝離。

門區的形成

步驟12 - 氧化過程:在晶片上沉積氧化層,該氧化層用作進一步擴散和金屬化過程的屏蔽。

氧化過程

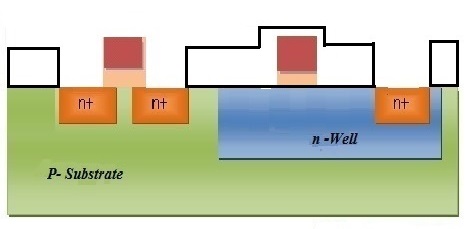

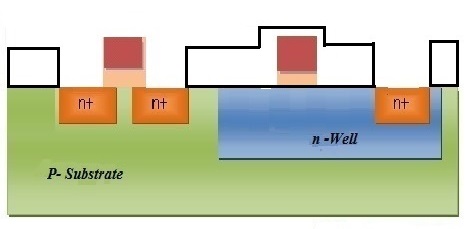

步驟13 - 掩蔽和擴散:為了使用掩模工藝制造用于擴散n型雜質的區域,進行小間隙。

掩蔽

使用擴散工藝開發了三個n +區域用于形成NMOS晶體管的端子。

N型擴散

步驟14 - 去除氧化物:剝離氧化物層。

去除氧化物

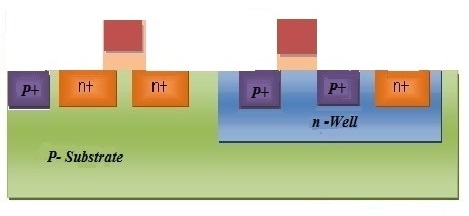

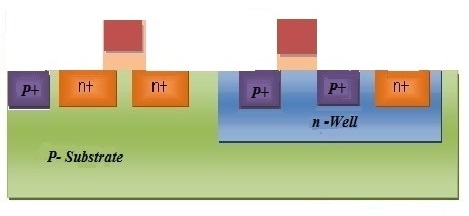

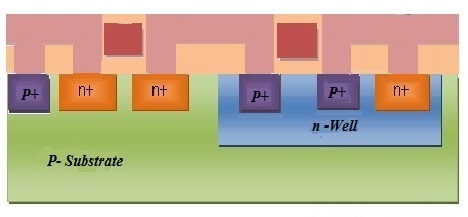

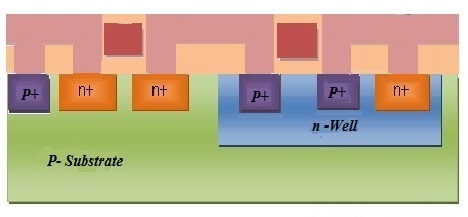

步驟15 - P型擴散:類似于用于形成PMOS晶體管 p型擴散的端子的n型擴散。

P型擴散

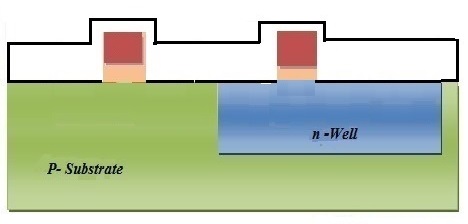

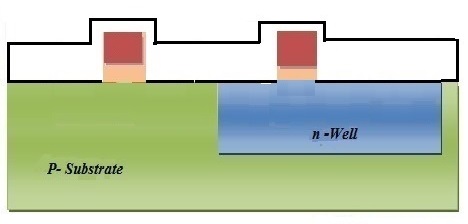

步驟16 - 厚場氧化物的鋪設:在形成金屬端子之前,布置厚場氧化物以形成用于晶片區域的保護層,其中不需要端子。

厚場氧化層

步驟17 - 金屬化:該步驟用于形成可提供互連的金屬端子。鋁散布在整個晶圓上。

金屬化

步驟18 - 去除多余金屬:從晶片上除去多余的金屬。

步驟19 - 端子的形成:在去除多余金屬端子之后形成的間隙中形成用于互連的端子。

終端的形成

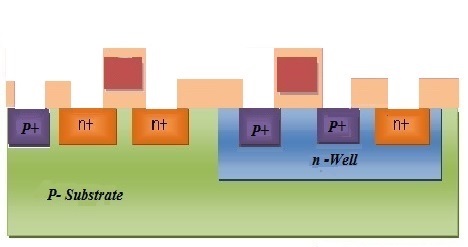

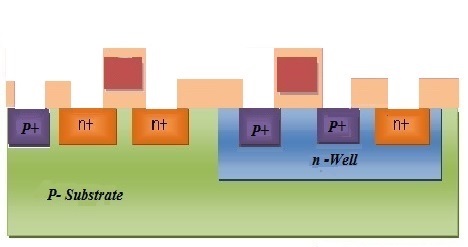

步驟20 - 分配端子名稱:將名稱分配給NMOS管和PMOS晶體管的端子。

分配終端名稱

利用P阱技術制作CMOS晶體管

p阱工藝類似于N阱工藝,除了在此使用n型襯底并且進行p型擴散。通常,為簡單起見,優選N阱工藝。

雙管制造CMOS晶體管

使用雙管工藝可以控制P和N型器件的增益。使用雙管法制造CMOS晶體管所涉及的各種步驟如下:

• 采用輕摻雜的n或p型襯底并使用外延層。外延層保護芯片中的閂鎖問題。

• 生長具有測量厚度和精確摻雜劑濃度的高純硅層。

• P和N井管的形成。

• 薄氧化物結構,用于防止擴散過程中的污染。

• 使用離子注入方法形成源極和漏極。

• 切割用于制造金屬觸點的部分。

• 進行金屬化以繪制金屬觸點。

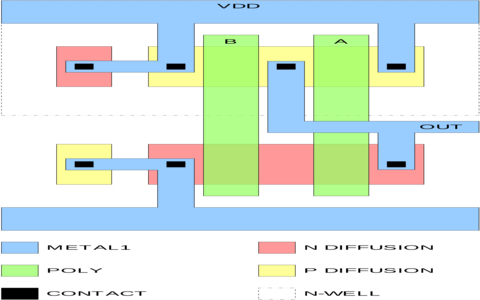

CMOS晶體管 IC布局

給出了CMOS晶體管制造和布局的上視圖 。這里可以清楚地看到各種金屬觸點和N阱擴散。

CMOS晶體管 IC布局

因此,這完全與CMOS晶體管制造技術有關。讓我們考慮將1平方的晶片分成400個芯片,表面積為50密耳×50密耳。制造晶體管需要50平方毫米的面積。因此,每個IC包含2個晶體管,因此在每個晶片上構建有2×400 = 800個晶體管。如果每批處理10個晶片,則可以同時制造8000個晶體管。您在IC上觀察到了哪些組件?

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹