近年來,隨著各類電子系統(tǒng)的高功能和高性能化,IC芯片的消耗電流量越來越大。另一方面,IC的高功能化推動了內(nèi)部結(jié)構(gòu)的精細化,因此IC的耐電壓下降,電源電壓值下降。看近年來的趨勢,需要減少電壓波動,而另一方面,IC消耗電流變化又在增加。因此,需要進一步降低另一個因素——阻抗。

本文以TDK公司的技術(shù)注釋(AN)為基礎(chǔ),介紹通過活用電源完整性(PI)將兩端子MLCC(積層陶瓷貼片電容)改為低ESL產(chǎn)品,以降低電源線路阻抗和減少去耦電容數(shù)量。

1. 低電壓/大電流電源線的去耦電容

隨著電源電壓值的下降,為了抑制電壓波動,降低電源線路的阻抗顯得越來越重要。為了在基板尺寸以及貼裝區(qū)域等受到嚴格限制的情況下,實現(xiàn)系統(tǒng)需要的阻抗特性,TDK提出了將MLCC替換為低ESL產(chǎn)品來減少去耦電容數(shù)量的方案。

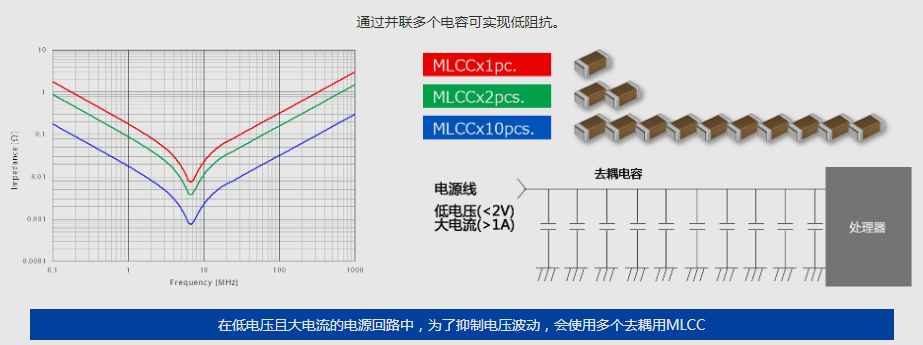

同時,由于電子設備系統(tǒng)的高功能化和高速動作化,系統(tǒng)內(nèi)部數(shù)字IC用電源線路的特性(PI:電源完整性)顯得越來越重要。提高PI的關(guān)鍵在于降低電源線路的阻抗,因此,在低電壓且大電流的電源回路中,會使用大量的MLCC作為去耦電容,通過并聯(lián)多個電容來實現(xiàn)低阻抗。

但是,隨著安裝小型化,對基板尺寸和貼裝區(qū)域的限制越發(fā)嚴格,已很難為了得到期望的阻抗特性而大量貼裝必要的MLCC。

不同并聯(lián)貼裝數(shù)量的MLCC阻抗頻率特性圖

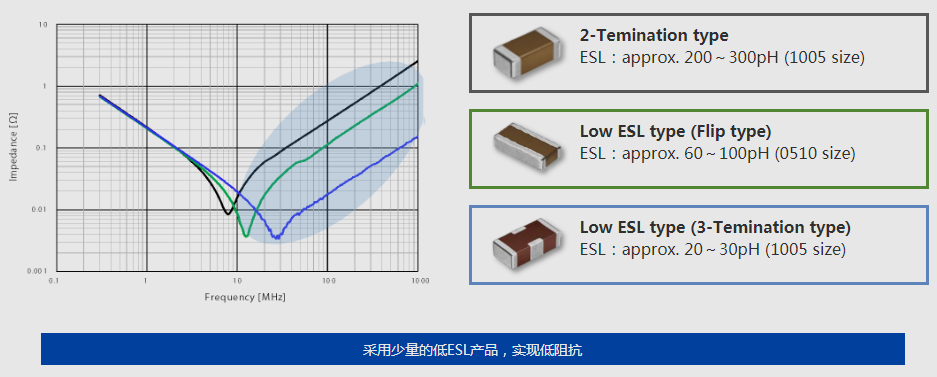

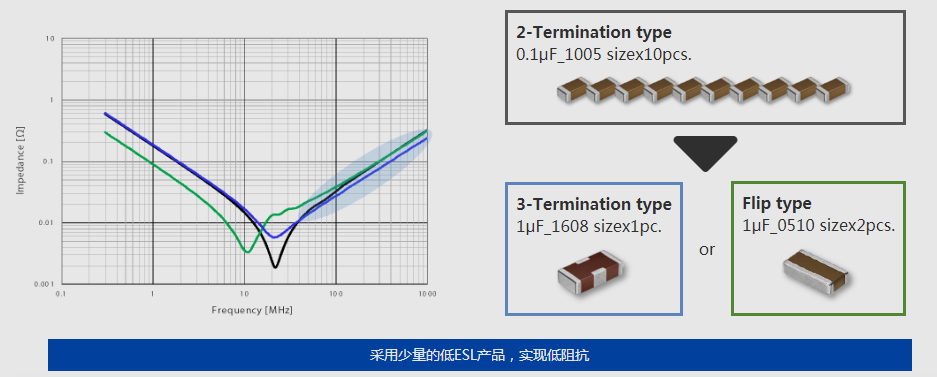

2. 采用少量的低ESL產(chǎn)品,實現(xiàn)低阻抗

一個有效的解決方法是,采用少量的低ESL產(chǎn)品,實現(xiàn)低阻抗。根據(jù)TDK公司的建議,采用低ESL型電容能夠降低去耦電容的數(shù)量和減少貼裝面積。低ESL型電容是低電感成分(ESL)的產(chǎn)品,在從低頻到高頻的寬頻帶實現(xiàn)了低阻抗。因此,大量使用通常型電容才能實現(xiàn)阻抗特性,低ESL型電容只需很少的數(shù)量即可實現(xiàn)。

典型低ESL產(chǎn)品的阻抗頻率特性

通常10個2端子產(chǎn)品 vs 1~2個低ESL產(chǎn)品的阻抗頻率特性

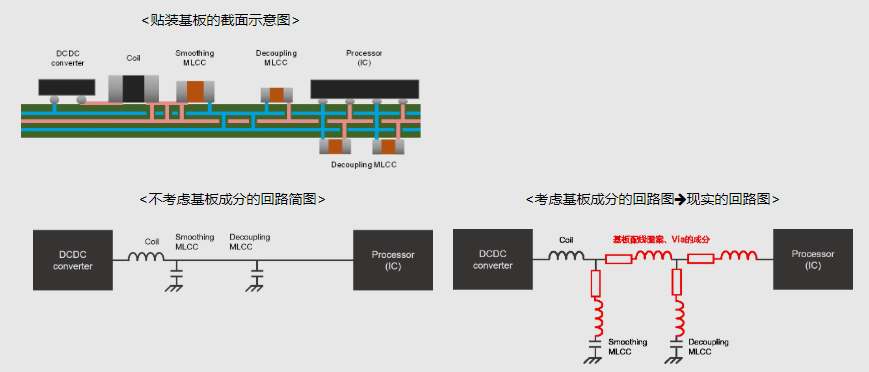

3. 基板配線圖案也是電路的一部分

除了去耦電容的最佳選定和最佳結(jié)構(gòu)化之外,貼裝基板的圖案設計對電源線路的低阻抗化也有重要作用。貼裝基板的線路用導體圖案和通孔中存在電阻成分、寄生電感和雜散電容,在電源線路的阻抗設計中,基板本身的電氣成分也需要作為阻抗成分的一部分在基板圖案設計中加以考慮。

通常DC-DC轉(zhuǎn)換器和IC(Processor)之間的回路示意圖

一般來說,隨著基板設計的深入而會出現(xiàn)各種制約,需要根據(jù)基板類型/貼裝面/IC Pin Layout/周邊元器件布局等貼裝基板結(jié)構(gòu),來選定最佳的電容類型、數(shù)量結(jié)構(gòu)、基板線路式樣、元器件排版等提供方案。例如,在基板圖案設計正式開始之前,TDK也可對需要的MLCC去耦電容數(shù)量、無法將MLCC配置在IC附近時的容許距離等進行驗證和提案,解決用戶電源線路設計方面的困擾。

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹