CMOS(cornplementary MOS)由成對的互補p溝道與n溝道MOSFET所組成.CMoS邏輯成為目前集成電路設計最常用技術的緣由,在于其有低功率損耗以及較佳的噪聲抑止才干.事實上,由于低功率損耗的需求,目前僅有CMOS技術被運用于ULSI的制造.

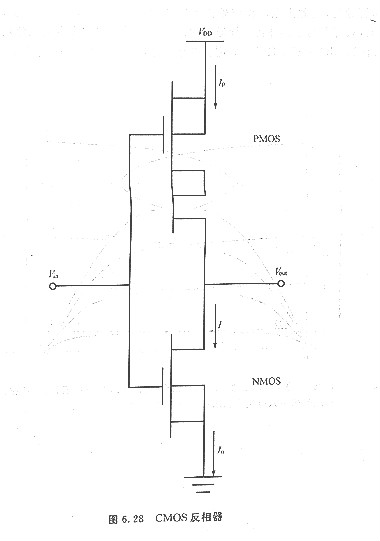

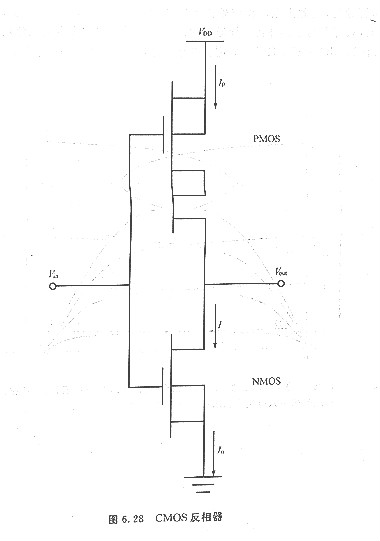

6.4.1CMOS反相器

如圖6. 28所示,CMOS反相器為CMOS邏輯電路的基本單元.在CMOS反相器中,p與n溝道晶體管的柵極銜接在一同,并作為此反相器的輸入端,而此二晶體管的漏極也連接在一同,并作為反相器的輸出端.n溝道MOSFET的源極與襯底接點均接地,而p溝道MOSFET的源極與襯底則銜接至電源供應端(VDD),需留意的是p溝道與n溝道MOSFET均為增強型晶體管,當輸入電壓為低電壓時(即vin=O,VGsn=o|VTp|(VGSp與VTp為負值),所以p溝道MOSFET.為導通態,

因此,輸出端經過p溝道MOSFET充電至VDD,當輸入電壓逐漸升高,使柵極電壓等于VDD時,由于VGSn=VDD>VTn,所以n溝道MOSFET將被導通,而由于|VGSp |≈O<|VTp|,所以p溝道MOSFET將被關閉.因此輸出端將經n溝道MOSFET放電至零電勢,

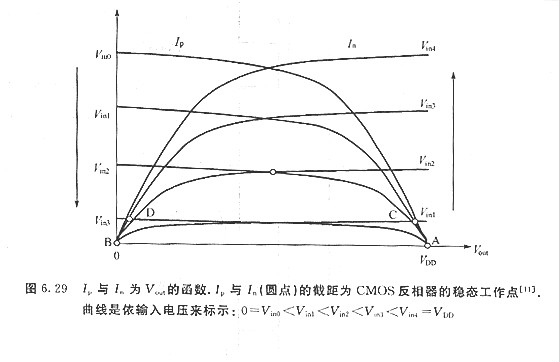

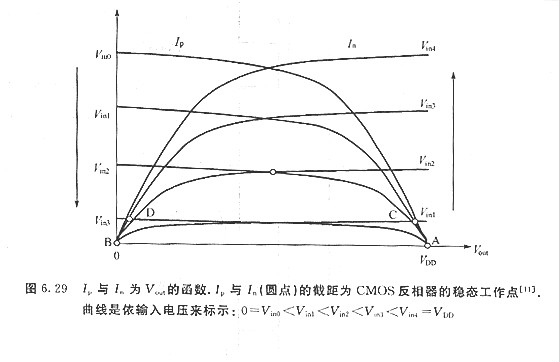

欲更深化天文解CMOS反相器的工作,可先畫出晶體管的輸出特性,如圖6.29所示,其中顯現Ip以及In為輸出電壓(Vout)函數.Ip為p溝道MOSFET由源極(銜接至VDD)流向漏極(輸出端)的電流;In為n溝道MOSFET由漏極(輸出端)流向源極(銜接至接地端)

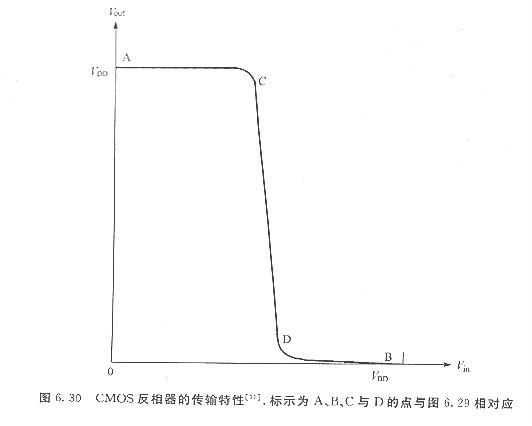

的電流.需留意的是在固定Vout下,增加輸入電壓(vin)將會增加In而減少Ip,但是在穩態時,In應與Ip相同,關于給定一個Vin可由In(Vin)與Ip(Vin)的截距,計算出相對應的Vout如圖6. 29所示.如圖6.30所示的Vin-Vout曲線稱為CMOS反相器的傳輸曲線.

CMOS反相器的一個重要的特性是,當輸出處于邏輯穩態(即Vout=或VDD)時,僅有一個晶體管導通,因此由電源供應處流到地端的電流非常小,且相當于器件關閉時的漏電流.事實上,只需在兩個器件暫時導通時的極短暫態時間內才會有大電流流過,因此與其他種類如n溝道MOSFET、雙極型等邏輯電路相比,其穩態時的功率損耗甚低.

烜芯微專業制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹