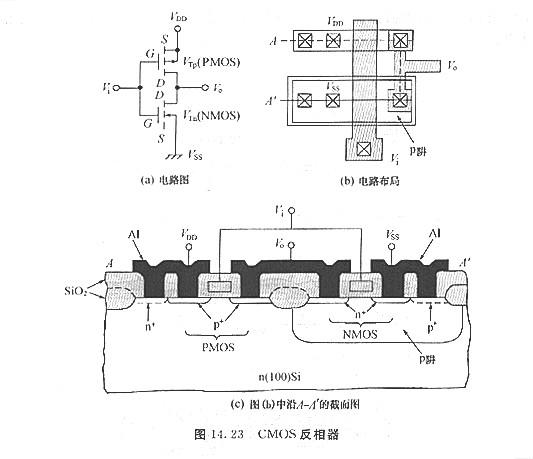

圖14.23(a)為- CMOS反相器,上方PMOS的柵極與下方NMOS的柵極相連,兩種器件皆為加強型MOSFET;對PMOS器件而言,閾值電壓VTn小于零,而對NMOS器件而言,閾值電壓VTn大于零(通常閾值電壓約為1/4VDD).當輸入電壓Y1為接地或是小的正電壓時,PMOS器件導通(PMOS柵極-地間的電勢為-VDD,較vTp更小),而NMOS為關閉狀態.因而,輸出電壓Vo十分接近VDD。(邏輯1).當輸入為VDD時,PMOS(Vcs=0)為關閉狀態,而NMOS為導通狀態(Vi=VDD,>VTn).所以,輸㈩電壓Vn等于零(邏輯),CMOS反相器有一個共同的特性:即在任一的邏輯狀態,在由VDD到接地間的串聯途徑上,其中有一個器件是不導通的,因而在任一穩定邏輯狀態下,只要小的漏電流;只要在MOS開關電源狀態時,兩個器件才會同時導通,也才會有明顯的電流流過CMOS反相器.因而,均勻功率耗費相當小,只要幾納瓦,當每個芯片上的器件數日增加時,功率耗費變成一個主要限制要素.低功率耗費就成為CMOS電路最吸收人的特征.

圖14. 23(b)為CMOS反相器的規劃.圖14.23(c)則為沿著A-A,的器件截面圖,在這個工藝中,先在n型襯底上停止p型注入摻雜而構成一個P型阱(或p型槽).p型摻雜濃度必需足夠高才干過度補償(overcompensate)n型襯底的背景濃度(backgrounddoping).關于p型阱的n溝道MOSFET,工藝則與前面所提過的相同,關于p溝道MOSFET而言,注入B、或(BF2)、離子至n型襯底構成源極與漏極,而As+離子則可用于溝道離子注入來調整閾值電壓及在p溝道器件左近的場氧化層下構成n+溝道阻斷,由于制造p溝道MOS-FET需求p阱和其他的步驟,所以制造CMOS電路的工藝步驟數是NMOS電路的兩倍,因而,我們在工藝復雜性與降低功率耗費間需有所取舍,

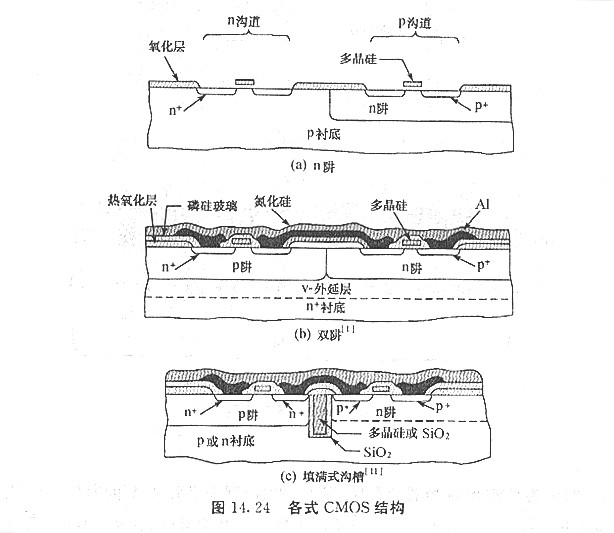

除了上述的1,阱,另一個替代辦法是在1,型襯底內構成n阱,如圖14.24(a)所示.在這個,隋況下,n型摻雜濃度必需足夠高才干過度補償p型襯底的背景濃度(即ND>NA).不論用p阱還是n阱,在阱中的溝道遷移率會衰退,由于遷移率是由全部摻雜濃度(NA十ND)決議的.最近有一種辦法為在輕摻雜的襯底內注入兩個別離的阱,如圖14. 24(b)所示.這個構造稱為雙阱(twin tubs).由于在任一阱中都不需求過度補償,所以能夠得到較高的遷移率。

一切CMOS電路都有寄生雙極型晶體管所惹起的閂鎖(latchup,或譯栓鎖)問題.一個可有效防止閂鎖問題的工藝技術為運用深溝槽隔離( deep trench isola-tion),如圖14. 24(c)所示,在此技術中,應用各向異性反響離子濺射刻(anisotropicreactivesputteretching)刻蝕出一個比阱還要深的隔離溝槽.接著在溝槽的底部和側壁上生長熱氧化層,然后淀積多晶硅或二氧化硅以將溝槽填滿,這個技術消弭了閂鎖現象,由于n溝道與p溝道器件被深溝槽隔分開來,以下將討論關于溝槽隔離的細致步驟與相關的CMOS工藝.

烜芯微專業制造二極管,三極管,MOS管,橋堆20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹