邏輯器件中,決定交接信號的規格是由作為DC電學特性的輸入電壓肯定的。輸入電壓存在兩種規格:將輸入斷定為“L”的低電平輸入電壓(VIL),和輸入斷定為“H”的高電平輸入電壓(VIH)。邏輯器件是處置、傳送2值邏輯的,所以信號處置必需可以判別“L”或者“H”(“0”或者“1”)。

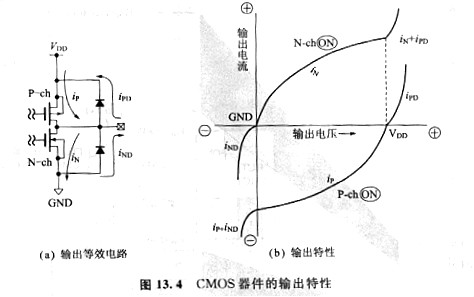

表13.3列出邏輯器件最典型的輸入電壓的規格。電源電壓為5V的電子設備中,要按CMOS電平或者TTL電平停止設計。為什么存在兩種規格?這是由于CMOS與雙極的電路構造不同。世界上首先降生的邏輯器件是TTL。TTL長期作為邏輯電路的主流被運用著。后來的CMOS在開展過程中逐步樹立起CMOS本人的規格設定,這是歷史緣由構成的。

CMOS在與TTL有相同電源電壓環境中運用時,設置的信號電平關于TTL沒有不適宜。反過來關于不希望在變換CMOS電平上花時間用戶來說,在規范CMOS邏輯條件要留意TTL輸入產品(74VHCT**,74HCT**型)。CMOS定制IC和CMOS存儲器等中,也大量存在用TTL信號電平規格化的產品。

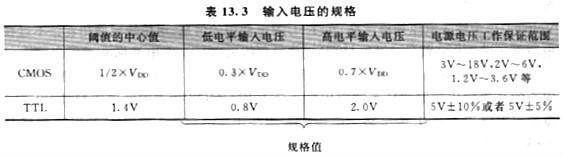

圖13.5就規范邏輯的CMOS(以74HC、74VHC為代表)與TTL( 74LS、74ALS),將電源電壓與輸入輸出電壓的DC規格圖解化。能夠看出,關于“L”電平CMOS與TTL有可以互相接口的規格。關于“H”電平,TTL的輸入端能夠承受CMOS的輸出,不過TTL的輸出卻不能被CMOS輸入承受。但是,能夠看出CMOS的“74**xT型”中,輸入、輸出都可以與TTL接口,沒有什么問題。

CMOS器件與TTL不同,由于工作電源電壓范圍寬,以5V單一-電源為前提設定的TTL電平(VIL=0.8V,VIH=2.0V/絕對值),用同一器件,要適用更低的電源電壓是很勉強的。例如,CMOS規范邏輯的恣意系列中,要使電源電壓為5V時的輸入電壓規格值與電源電壓為2V時的輸入電壓規格值相等是不容易的。

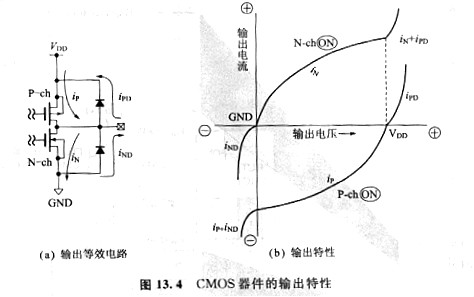

CMOS器件中,即便電源電壓的運用環境有很大變化,由于輸入電壓經常設計為電源電壓的l/2(50%Vcc),所以容易與其他器件接口,也能提供確保抗噪聲容量(距GND電平或者從電源電平)的性能。

烜芯微專業制造二極管,三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹