MOSFET

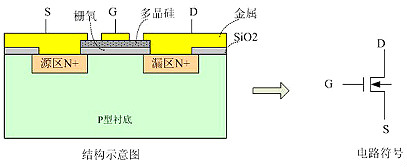

MOSFET簡稱金氧半場效晶體管(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)是一種可以廣泛使用在模擬電路與數字電路的場效晶體管(field-effect transistor)。MOSFET依照其“通道”(工作載流子)的極性不同,可分為“N型”與“P型” 的兩種類型,通常又稱為NMOSFET與PMOSFET,其他簡稱尚包括NMOS、PMOS等。

MOSFET的主要參數

場效應管的參數很多,包括直流參數、交流參數和極限參數,但一般使用時關注以下主要參數:

1、IDSS—飽和漏源電流。是指結型或耗盡型絕緣柵場效應管中,柵極電壓UGS=0時的漏源電流。

2、UP—夾斷電壓。是指結型或耗盡型絕緣柵場效應管中,使漏源間剛截止時的柵極電壓。

3、UT—開啟電壓。是指增強型絕緣柵場效管中,使漏源間剛導通時的柵極電壓。

4、gM—跨導。是表示柵源電壓UGS—對漏極電流ID的控制能力,即漏極電流ID變化量與柵源電壓UGS變化量的比值。gM是衡量場效應管放大能力的重要參數。

5、BUDS—漏源擊穿電壓。是指柵源電壓UGS一定時,場效應管正常工作所能承受的最大漏源電壓。這是一項極限參數,加在場效應管上的工作電壓必須小于BUDS。

6、PDSM—最大耗散功率。也是一項極限參數,是指場效應管性能不變壞時所允許的最大漏源耗散功率。使用時,場效應管實際功耗應小于PDSM并留有一定余量。

7、IDSM—最大漏源電流。是一項極限參數,是指場效應管正常工作時,漏源間所允許通過的最大電流。場效應管的工作電流不應超過IDSM。

如何做到電源設計減少MOS管損耗的同時提升EMI性能

MOSFET作為主要的開關功率器件之一,被大量應用于模塊電源。了解MOSFET的損耗組成并對其分析,有利于優化MOSFET損耗,提高模塊電源的功率;但是一味的減少MOSFET的損耗及其他方面的損耗,反而會引起更嚴重的EMI問題,導致整個系統不能穩定工作。所以需要在減少MOSFET的損耗的同時需要兼顧模塊電源的EMI性能。

開關管MOSFET的功耗分析

MOSFET的損耗主要有以下部分組成:1.通態損耗;2.導通損耗;3.關斷損耗;4.驅動損耗;5.吸收損耗;隨著模塊電源的體積減小,需要將開關頻率進一步提高,進而導致開通損耗和關斷損耗的增加,例如300kHz的驅動頻率下,開通損耗和關斷損耗的比例已經是總損耗主要部分了。

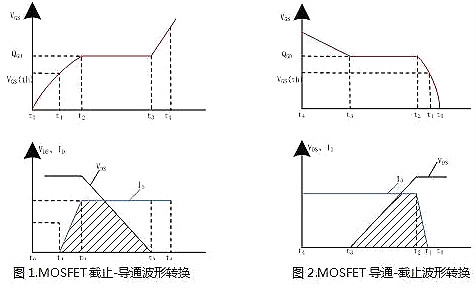

MOSFET導通與關斷過程中都會產生損耗,在這兩個轉換過程中,漏極電壓與漏極電流、柵源電壓與電荷之間的關系如圖1和圖2所示,現以導通轉換過程為例進行分析:

t0-t1區間:柵極電壓從0上升到門限電壓Uth,開關管為導通,無漏極電流通過這一區間不產生損耗;

t1-t2區間:柵極電壓達到Vth,漏極電流ID開始增加,到t2時刻達到最大值,但是漏源電壓保持截止時高電平不變,從圖1可以看出,此部分有VDS與ID有重疊,MOSFET功耗增大;

t2-t3區間:從t2時刻開始,漏源電壓VDS開始下降,引起密勒電容效應,使得柵極電壓不能上升而出現平臺,t2-t3時刻電荷量等于Qgd,t3時刻開始漏極電壓下降到最小值;此部分有VDS與ID有重疊,MOSFET功耗增大

t3-t4區間:柵極電壓從平臺上升至最后的驅動電壓(模塊電源一般設定為12V),上升的柵壓使導通電阻進一步減少,MOSFET進入完全導通狀態;此時損耗轉化為導通損耗。

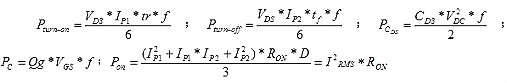

關斷過程與導通過程相似,只不過是波形相反而已;關于MOSFET的導通損耗與關斷損耗的分析過程,有很多文獻可以參考,這里直接引用《張興柱之MOSFET分析》的總結公式如下:

MOSFET的損耗優化方法及其利弊關系

(一)

通過降低模塊電源的驅動頻率減少MOSFET的損耗,EMI問題及其解決方案。

(二)通過降低、來減少MOSFET的損耗

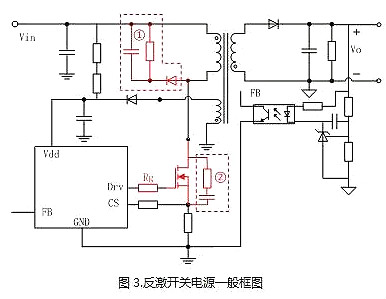

典型的小功率模塊電源(小于50W)大多采用的電路拓撲結構為反激形式,典型的控制電路如圖3所示;從MOSFET的損耗分析還可以知道:與開通損耗成正比、與關斷損耗成正比;所以可以通過減少 、來減少MOSFET的損耗,通常情況下,可以減小MOSFET的驅動電阻Rg來減少、時間,但是此優化方法卻帶來嚴重的EMI問題;以金升陽URB2405YMD-6WR3產品為例來說明此項問題:

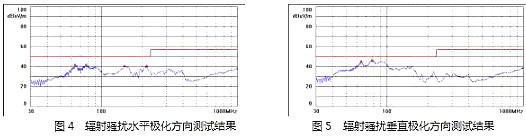

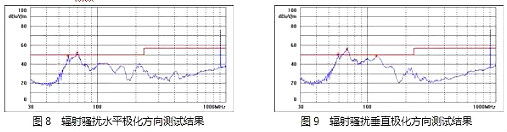

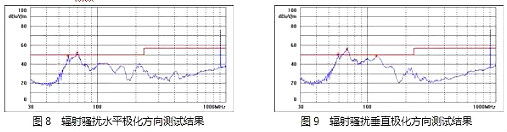

1)URB2405YMD-6WR3采用10Ω的MOSFET驅動電阻,裸機輻射測試結果如下:

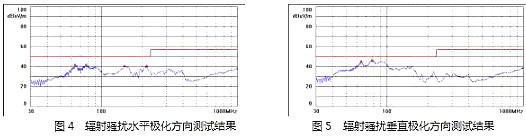

2)URB2405YMD-6WR3采用0Ω的驅動電阻,裸機輻射測試結果如下:

從兩種不同的驅動電阻測試結果來看,雖然都能夠通過EN55022的輻射騷擾度的CLASS A等級,但是采用0歐姆的驅動電阻,在水平極化方向測試結果的余量是不足3dB的,該方案設計不能被通過。

(三)降低吸收電路損耗來減少損耗

在模塊電源的設計過程中,變壓器的漏感總是存在的,采用反激拓撲式結構,往往在MOSFET截止過程中,MOSFET的漏極往往存在著很大的電壓尖峰,一般情況下,MOSFET的電壓設計余量是足夠承受的,為了提高整體的電源效率,一些電源廠家是沒有增加吸收電路(吸收電路如圖3標注①RCD吸收電路和②RC吸收電路)來吸收尖峰電壓的。但是,不注意這些吸收電路的設計往往也是導致EMI設計不合格的主要原因。以金升陽URF2405P-6WR3的吸收電路(采用如圖3中的②RC吸收電路)為例:

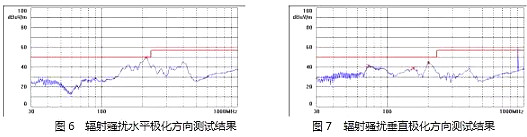

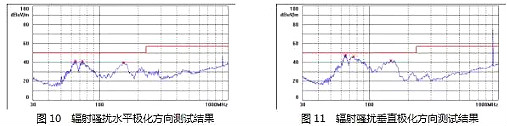

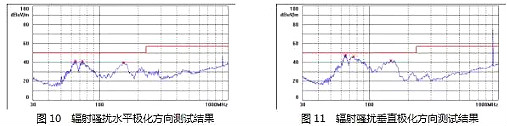

1)驅動電阻Rg為27Ω,無RC吸收電路,輻射騷擾度測試結果如下:

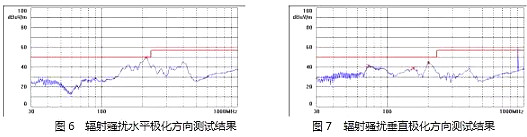

2)驅動電阻為27Ω;吸收電路為電阻R和C 5.1Ω 470pF,輻射騷擾度測試結果如下:

從兩種不同的吸收電路方案測試結果來看,不采用吸收電路的方案,是不能通過EN55022輻射騷擾度的CLASS A等級,而采用吸收電路,則可以解決輻射騷擾度實驗不通過的問題,通過不同的RC組合方式可進一步降低輻射騷擾。

MOSFET的功耗優化工作實際上是一個系統工程,部分優化方案甚至會影響EMI的特性變化。上述案例中,金升陽R3系列產品將節能環保的理念深入到電源的開發過程中,很好地平衡了電源整體效率與EMI特性,從而進一步優化了電源參數。將電源參數進一步優化,更能兼容客戶系統,并發揮真正的電子系統“心臟”作用,源源不斷的輸送能量。

如何減少mos管損耗的方法

1、晶體管緩沖電路

早期電源多采用此線路技術。采用此電路,功率損耗雖有所減小,但仍不是很理想。

①減少導通損耗在變壓器次級線圈后面加飽和電感,加反向恢復時間快的二極管,利用飽和電感阻礙電流變化的特性,限制電流上升的速率,使電流與電壓的波形盡可能小地重疊。

②減少截止損耗加R、C吸收網絡,推遲變壓器反激電壓發生時間,最好在電流為0時產生反激電壓,此時功率損耗為0。該電路利用電容上電壓不能突變的特性,推遲反激電壓發生時間。為了增加可靠性,也可在功率管上加R、C。但是此電路有明顯缺點:因為電阻的存在,導致吸收網絡有損耗。

2、諧振電路

該電路只改變開關瞬間電流波形,不改變導通時電流波形。只要選擇好合適的L、C,結合二極管結電容和變壓器漏感,就能保證電壓為0時,開關管導通或截止。因此,采用諧振技術可使開關損耗很小。所以,SWITCHTEC電源開關頻率可以做到術結構380kHz的高頻率。

3、軟開關技術

該電路是在全橋逆變電路中加入電容和二極管。二極管在開關管導通時起鉗位作用,并構成瀉放回路,瀉放電流。電容在反激電壓作用下,電容被充電,電壓不能突然增加,當電壓比較大的時侯,電流已經為0。

烜芯微專業制造二三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹